TELECOMMUNICATION STANDARDIZATION SECTOR OF ITU

# SERIES K: PROTECTION AGAINST INTERFERENCE

Surge protective component application guide – Silicon PN junction components

Recommendation ITU-T K.103

**T-UT**

## **Recommendation ITU-T K.103**

## Surge protective component application guide – Silicon PN junction components

#### Summary

Recommendation ITU-T K.103 describes the construction, characteristics, ratings and application examples of surge protective components (SPCs), having one or two silicon PN junctions, intended for the protection of exchange and outdoor equipment, subscriber or customer equipment and telecommunication lines from surges. The PN junction technologies covered are: Zener breakdown, avalanche breakdown, fold-back, punch-through and rectification.

#### History

| Edition | Recommendation | Approval   | Study Group | Unique ID*         |

|---------|----------------|------------|-------------|--------------------|

| 1.0     | ITU-T K.103    | 2015-03-01 | 5           | 11.1002/1000/12423 |

#### Keywords

Application circuits, array, avalanche, electrical characteristics, electrical ratings, fold-back, punch-through, rectification, Zener.

<sup>\*</sup> To access the Recommendation, type the URL http://handle.itu.int/ in the address field of your web browser, followed by the Recommendation's unique ID. For example, <u>http://handle.itu.int/11.1002/1000/11</u> <u>830-en</u>.

#### FOREWORD

The International Telecommunication Union (ITU) is the United Nations specialized agency in the field of telecommunications, information and communication technologies (ICTs). The ITU Telecommunication Standardization Sector (ITU-T) is a permanent organ of ITU. ITU-T is responsible for studying technical, operating and tariff questions and issuing Recommendations on them with a view to standardizing telecommunications on a worldwide basis.

The World Telecommunication Standardization Assembly (WTSA), which meets every four years, establishes the topics for study by the ITU-T study groups which, in turn, produce Recommendations on these topics.

The approval of ITU-T Recommendations is covered by the procedure laid down in WTSA Resolution 1.

In some areas of information technology which fall within ITU-T's purview, the necessary standards are prepared on a collaborative basis with ISO and IEC.

#### NOTE

In this Recommendation, the expression "Administration" is used for conciseness to indicate both a telecommunication administration and a recognized operating agency.

Compliance with this Recommendation is voluntary. However, the Recommendation may contain certain mandatory provisions (to ensure, e.g., interoperability or applicability) and compliance with the Recommendation is achieved when all of these mandatory provisions are met. The words "shall" or some other obligatory language such as "must" and the negative equivalents are used to express requirements. The use of such words does not suggest that compliance with the Recommendation is required of any party.

#### INTELLECTUAL PROPERTY RIGHTS

ITU draws attention to the possibility that the practice or implementation of this Recommendation may involve the use of a claimed Intellectual Property Right. ITU takes no position concerning the evidence, validity or applicability of claimed Intellectual Property Rights, whether asserted by ITU members or others outside of the Recommendation development process.

As of the date of approval of this Recommendation, ITU had not received notice of intellectual property, protected by patents, which may be required to implement this Recommendation. However, implementers are cautioned that this may not represent the latest information and are therefore strongly urged to consult the TSB patent database at <u>http://www.itu.int/ITU-T/ipr/</u>.

#### © ITU 2015

All rights reserved. No part of this publication may be reproduced, by any means whatsoever, without the prior written permission of ITU.

## **Table of Contents**

## Page

| 1      | Scope     |                                                            | 1  |  |  |

|--------|-----------|------------------------------------------------------------|----|--|--|

| 2      | Referen   | ces                                                        | 1  |  |  |

| 3      | Definitio | ons                                                        | 1  |  |  |

|        | 3.1       | Terms defined elsewhere                                    | 1  |  |  |

|        | 3.2       | Terms defined in this Recommendation                       | 2  |  |  |

| 4      | Abbrevi   | ations and acronyms                                        | 2  |  |  |

| 5      | Convent   | entions                                                    |    |  |  |

| 6      | Constru   | ction                                                      | 3  |  |  |

|        | 6.1       | Packaging                                                  | 3  |  |  |

|        | 6.2       | Semiconductor junction structure and electrical properties | 4  |  |  |

| 7      | Characte  | eristics                                                   | 10 |  |  |

|        | 7.1       | Stand-off or maximum reverse working voltage, VRWM         | 11 |  |  |

|        | 7.2       | Breakdown voltage, V <sub>(BR)</sub>                       | 11 |  |  |

|        | 7.3       | Clamping voltage, VC                                       | 12 |  |  |

|        | 7.4       | Punch-through voltage $V_{(PT)}$                           | 13 |  |  |

|        | 7.5       | Snap back voltage $V_{(SB)}$                               | 13 |  |  |

|        | 7.6       | Forward biased PN junction voltage, VF                     | 13 |  |  |

|        | 7.7       | Junction capacitance, CJ                                   | 15 |  |  |

|        | 7.8       | Package inductance                                         | 17 |  |  |

| 8      | Ratings   |                                                            | 17 |  |  |

|        | 8.1       | Peak pulse current, IPP                                    | 17 |  |  |

|        | 8.2       | Maximum peak pulse power, PPPM                             | 19 |  |  |

|        | 8.3       | Power dissipation, PD                                      | 19 |  |  |

| 9      | Applicat  | tion examples                                              | 20 |  |  |

|        | 9.1       | Series connection                                          | 20 |  |  |

|        | 9.2       | Parallel connection                                        | 21 |  |  |

|        | 9.3       | DC supply protection                                       | 21 |  |  |

|        | 9.4       | Power frequency protection                                 | 23 |  |  |

|        | 9.5       | Signal protection                                          | 24 |  |  |

| Biblio | graphy    |                                                            | 29 |  |  |

## **Recommendation ITU-T K.103**

## Surge protective component application guide – Silicon PN junction components

### 1 Scope

This Recommendation in the surge protective component application guide series covers voltage limiting components, having one or two silicon PN junctions. These surge protective components (SPCs) are clamping type overvoltage protectors [b-ITU-T K.96]. Components covered in this Recommendation use the following PN junction technologies: Zener breakdown, avalanche breakdown, fold-back, punch-through and rectification. Guidance is given on construction, characteristics, ratings and application examples.

### 2 References

This Recommendation does not contain any normative references.

### **3** Definitions

#### 3.1 Terms defined elsewhere

This Recommendation uses the following terms defined elsewhere:

**3.1.1** avalanche breakdown (of a PN junction) [b-IEC 60050-521]: Breakdown that is caused by the cumulative multiplication of charge carriers in a semiconductor under the action of a strong electric field, which causes some carriers to gain enough energy to liberate new hole-electron pairs by ionization.

**3.1.2 bidirectional transistor** [b-IEC 60050-521]: Transistor, which has substantially the same electrical characteristics when the terminals normally designated as emitter and collector are interchanged.

**3.1.3 bipolar junction transistor** [b-IEC 60050-521]: Transistor having at least two junctions and whose functioning depends on both majority carriers and minority carriers.

**3.1.4 breakdown (of a reverse-biased PN junction)** [b-IEC 60050-521]: Phenomenon, the initiation of which is observed as a transition from a state of high dynamic resistance to a state of substantially lower dynamic resistance for increasing magnitude of reverse current.

**3.1.5 common mode conversion** [b-ITU-T K.96]: Process by which a differential mode electrical signal is produced in response to a common mode electrical signal.

**3.1.6 common mode surge** [b-ITU-T K.96]: Surge appearing equally on all conductors of a group at a given location.

NOTE 1 – The reference point for common mode surge voltage measurement can be a chassis terminal, or a local earth/ground point.

NOTE 2 – Common mode surge is also known as longitudinal surge or asymmetrical surge.

**3.1.7 differential mode surge** [b-ITU-T K.96]: Surge occurring between any two conductors or two groups of conductors at a given location.

NOTE 1 – The surge source maybe be floating, without a reference point or connected to reference point, such as a chassis terminal, or a local earth/ground point.

NOTE 2 – Differential mode surge is also known as metallic surge or transverse surge or symmetrical surge or normal surge.

**3.1.8 diode (semiconductor)** [b-IEC 60050-521]: Two-terminal semiconductor device having an asymmetrical voltage-current characteristic.

1

NOTE – Unless otherwise qualified, this term usually means a device with the voltage-current characteristic typical of a single PN junction.

**3.1.9 fold-back breakdown (of a bidirectional transistor)** [b-ITU-T K.96]: Re-entrant breakdown characteristic caused by transistor action producing a region of negative dynamic resistance before reverting back to a low positive dynamic resistance condition.

NOTE – In transistor terms, the initial breakdown is in the  $BV_{CBO}$  mode, which changes to the lower voltage  $BV_{CEO}$  mode as the breakdown current increases.

**3.1.10** overcurrent [b-ITU-T K.96]: Any current having a peak value exceeding the corresponding peak value of maximum steady-state current at normal operating conditions.

**3.1.11 overvoltage** [b-IEC 60664-2-1]: Any voltage having a peak value exceeding the corresponding peak value of maximum steady-state voltage at normal operating conditions.

**3.1.12** power fault [b-ITU-T K.96]: Abnormal fault condition, when the local AC power service is in electrical contact (power contact) or is magnetically coupled (power induction) to another service.

**3.1.13 PN junction** [b-IEC 61836]: Junction between a P-type semiconductor and an N-type semiconductor.

**3.1.14 punch-through (between two PN junctions)** [b-IEC 60050-521]: Contact between the space charge regions of two PN junctions as a result of widening of one or both of them.

**3.1.15** surge [b-ITU-T K.96]: Temporary disturbance on the conductors of an electrical service caused by an electrical event not related to the service.

NOTE – For non-linear SPCs a surge event is defined as an overvoltage or overcurrent or both.

**3.1.16** surge protective component (SPC) [b-ITU-T K.96]: Component specifically included in a device or equipment for the mitigation of the onward propagation of overvoltages or overcurrents or both.

**3.1.17 surge protective device (SPD)** [b-ITU-T K.96]: Device that mitigates the onward propagation of overvoltages or overcurrents or both.

**3.1.18 Zener breakdown (of a PN junction)** [b-IEC 60050-521]: Breakdown caused by the transition of electrons from the valence band to the conduction band due to tunnel action under the influence of a strong electric field in a PN junction.

Emitter

## **3.2** Terms defined in this Recommendation

None.

#### 4 Abbreviations and acronyms

This Recommendation uses the following abbreviations and acronyms:

| AC            | Alternating Current                         |

|---------------|---------------------------------------------|

| DC            | Direct Current                              |

| HDSL          | High-bit-rate Digital Subscriber Line       |

| HFE           | Hybrid model Forward current gain in common |

| IC            | Integrated Circuit                          |

| ICT           | Information and Communications Technology   |

| $I_{\rm PP}$  | Peak Pulse current                          |

| $I_{\rm PPM}$ | Maximum Peak Pulse current                  |

| $I_{ m R}$    | Reverse current                             |

| MOV                 | Metal-Oxide Varistor                          |

|---------------------|-----------------------------------------------|

| NASA                | National Aeronautics and Space Administration |

| PD                  | Powered Device                                |

| PHY                 | Physical Layer (usually Ethernet transceiver) |

| PLC                 | Power Line Communication                      |

| $P_{\mathrm{PPM}}$  | Maximum Peak Pulse Power                      |

| PSE                 | Power Sourcing Equipment                      |

| SDSL                | Symmetrical Digital Subscriber Line           |

| SELV                | Safety Extra Low Voltage                      |

| SPC                 | Surge Protective Component                    |

| SPD                 | Surge Protective Device                       |

| USB                 | Universal Serial Bus                          |

| $V_{(\mathrm{BR})}$ | Breakdown Voltage                             |

| $V_{\rm C}$         | Clamping Voltage                              |

| $V_{\rm CM}$        | Maximum Clamping Voltage                      |

| $V_{ m F}$          | Forward Voltage                               |

| $V_{(\text{PT})}$   | Punch-Through Voltage                         |

| $V_{ m R}$          | Reverse Voltage                               |

| $V_{\rm RWM}$       | Maximum Reverse Working Voltage               |

| $V_{(SB)}$          | Snapback Voltage                              |

#### 5 Conventions

None.

## 6 Construction

### 6.1 Packaging

There are two types of component packaging used with printed circuit boards: through-hole or surface-mount. Through-hole packaging is typically axial lead or side leaded. Surface-mount packaging may be leaded or with solderable pads. Figure 1 shows examples of these four package types.

Figure 1 – Example component packages (left to right): through-hole, axial and side leaded, surface-mount, leaded and pad

### 6.2 Semiconductor junction structure and electrical properties

This clause describes in simple terms the semiconductor chip structure, operation, circuit symbol and basic characteristics. For in depth information on these topics, text books on this subject, such as [b-Lindmayer] or [b-Baliga], should be referenced.

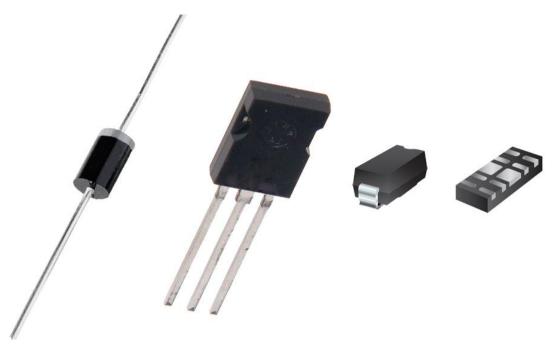

#### 6.2.1 Single PN junction structure and electrical characteristic

Figure 2 shows a diagram of a simple PN junction structure. Metallization is applied to the top and bottom of the structure for electrical contact. The N-type silicon region has negative carriers (electrons) and the P-type silicon region effectively has positive carriers (holes). The junction is formed where the material changes from N-type to P-type. A depletion layer is formed at the junction. The depletion region presents a threshold voltage that must be overcome before current can flow. If a voltage is applied with a positive polarity to the P region and negative polarity to the N region, for voltages above about 0.3 V, current will start to flow. Under these bias conditions the PN junction is termed as being forward biased. Voltages that exceed the threshold voltage will be limited to the forward voltage ( $V_{\rm F}$ ) characteristic value for the level of available current from the source of the voltage.

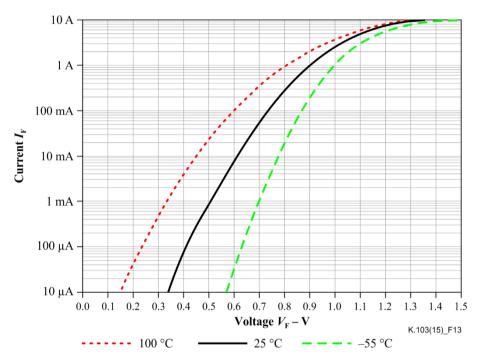

The Figure 2 graph shows an example of a PN junction forward biased characteristic plotted as forward current,  $I_F$ , against forward voltage,  $V_F$  over six decades of current. Above 1 A the voltage starts to increase rapidly as the material starts to run out of inherent current carriers.

The symbol shown next to the structure is for a general purpose rectifier diode.

Figure 2 – Forward biased PN junction structure, rectifier diode circuit symbol and electrical forward characteristic

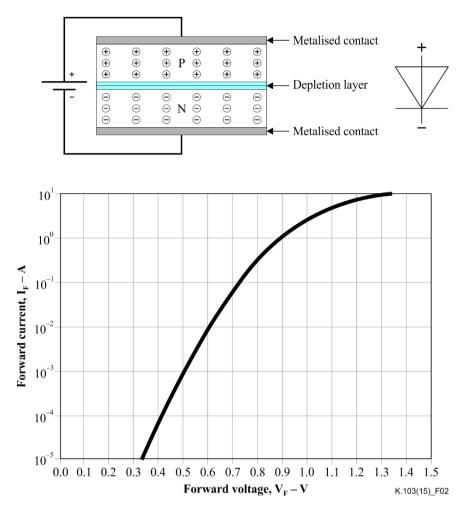

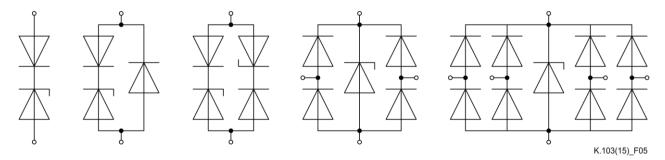

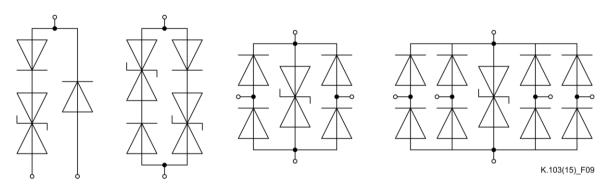

Single PN junction voltage limiting can only be used where either the signal is a few hundred millivolts or the signal or direct current (DC) supply is in the opposite polarity. The range of applications can be extended by using multiple diodes, either connecting the diodes in series or placing other diodes in the opposite polarity in parallel or both; see Figure 3. Four diodes can be used to create a bridge rectifier, useful to make unidirectional breakdown voltage ( $V_{(BR)}$ ) limiters into bidirectional voltage limiters.

A commercial example of the eight diode array has a total forward voltage of 2.4 V at 1 mA and 3.9 V at 1 A. Connecting four diodes in series reduces the array capacitance to 13 pF. The array has a 30 A 10/1000 rating.

**Figure 3 – Rectifier diode arrays**

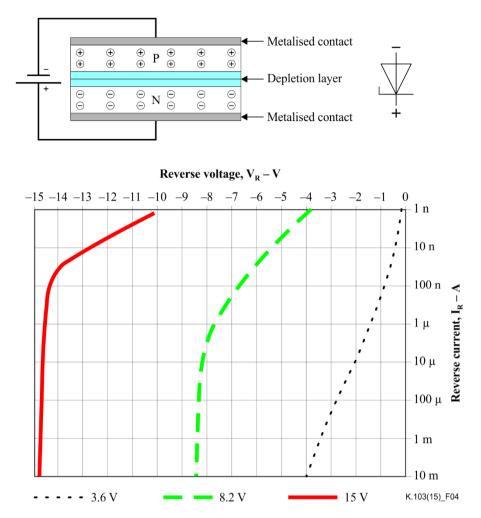

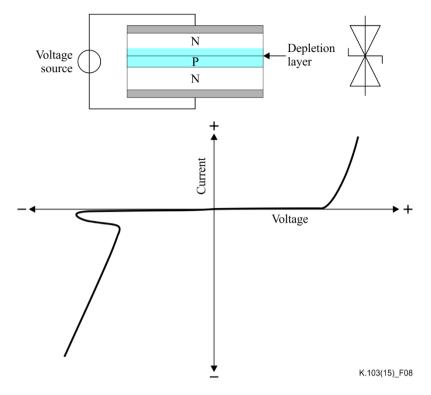

In Figure 4 the battery voltage is reversed compared with Figure 2. A negative polarity voltage is applied to the P region and a positive polarity voltage to the N region. The battery voltage adds to the natural depletion layer voltage and the depletion layer width expands to support the applied reverse voltage ( $V_R$ ). Under these bias conditions, the PN junction is termed as being reverse biased.

The Figure 4 graph shows an example of a PN junction reverse biased characteristic plotted as reverse current ( $I_R$ ) against reverse voltage,  $V_R$ , over seven decades of current. The three characteristics shown are for breakdown diodes with nominal breakdown voltages of 3.6 V, 8.2 V and 15 V. The differences among these characteristics are discussed in clause 7. Voltages that exceed the characteristic voltage will be limited to the  $V_R$  characteristic value for the level of available current from the source of the voltage.

The symbol shown next to the structure is for a PN junction component designed to be used in the reverse breakdown region. The small hook at the end of the diode symbol bar indicates a breakdown characteristic.

Figure 4 – Reverse biased PN junction structure, breakdown diode circuit symbol and electrical reverse characteristics

This structure has a breakdown characteristic in one voltage polarity and forward diode characteristic in the opposite voltage polarity. These voltage-limiting unidirectional diodes are available with breakdown voltages in the range of 5 V to 500 V and peak power ratings of 400 W to 5 kW. In restricted voltage ranges, higher power components of 30 kW are available.

Lower capacitance components can be produced by incorporating series and shunt rectifier diodes; see Figure 5. The unidirectional array is formed with series and shunt rectifiers. The bidirectional array uses two arms, each with a breakdown diode and rectifier. The bridged array uses four rectifier diodes in bridge connection and a breakdown diode. Further bridges can be added. For example four bridges can be used to protect eight digital integrated circuit (IC) signal connections. The bridged array has direct connections to the breakdown diode so that it can also protect a DC supply.

Figure 5 – PN voltage limiter low capacitance arrays: unidirectional, bidirectional, single bridged and double bridged

7

#### 6.2.2 NPN or PNP junction structures and electrical characteristics

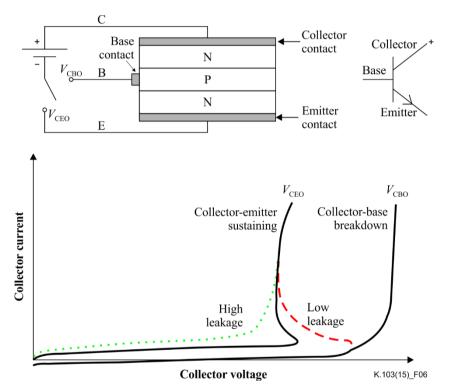

These three-layer voltage limiters are similar to NPN or PNP bipolar junction transistors without a base connection. A study of transistor characteristics is beneficial to understand how three-layer voltage limiters work.

Figure 6 shows an NPN transistor structure and the two collector-voltage characteristics. The top N-type layer is designated as the collector, the middle P-type layer is the base and the bottom N-type layer is the emitter. Test voltages are applied with two connection configurations: collector-base and collector-emitter. The collector-base voltage,  $V_{CBO}$  characteristic, with the emitter unconnected, has the same characteristic as a breakdown diode shown in Figure 4. The collector-emitter voltage,  $V_{CEO}$  characteristic, with the base unconnected, is lower in voltage at higher currents than the  $V_{CBO}$  characteristic by a factor dependent on the current gain ( $H_{FE}$ ) (collector current/base current) of the transistor. The  $V_{CEO}$  characteristic depends on the collector-base leakage current. For low levels of leakage current, the characteristic initially follows the  $V_{CBO}$  characteristic until breakdown current starts to flow. The breakdown current is a base current, which will be amplified by the transistor current gain,  $H_{FE}$ . As a result the collector-emitter voltage reduces to a lower sustaining level. As the level of leakage current increases low-current "toe" in the  $V_{CEO}$  characteristic gradually reduces to nothing, see the three  $V_{CEO}$  characteristics in Figure 6.

Figure 6 – NPN transistor structure, circuit symbol and electrical characteristics

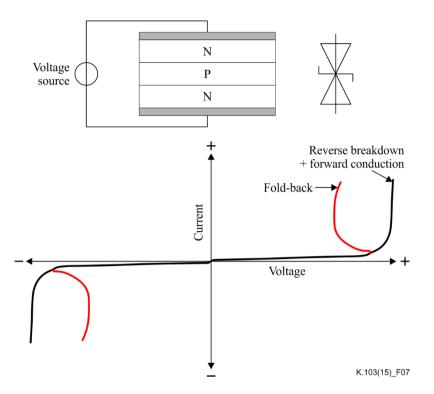

Three-layer voltage limiters, usually made symmetrical in structure, give bidirectional voltage limiting; see Figure 7. The circuit symbol is formed from two of the unidirectional symbols of Figure 4, connected in series and opposition.

This structure has similar breakdown characteristics in both voltage polarities and is termed bidirectional. These voltage limiting bidirectional diodes are available with breakdown voltages in the range of 5 V to 500 V and peak power ratings of 400 W to 5 kW. In restricted voltage ranges, higher power components of 30 kW are available.

Fold-back diodes have the limitation that the degree of fold-back ( $V_{CBO}$  to  $V_{CEO}$  difference) reduces at lower voltages. Consequently the typical voltage range starts at 30 V and ends at 500 V. Fold-back diodes are available with current ratings up to 10 kA 8/20.

Figure 7 - NPN voltage limiter structure, circuit symbol and electrical characteristics

Where the structure centre (P) layer is relatively thin, transistor action will occur resulting in a fold-back clamping characteristic like the  $V_{\text{CEO}}$  characteristic of Figure 6. When there is insignificant transistor action the clamping characteristic is the combination of the forward characteristic of Figure 2 and the  $V_{\text{CBO}}$  characteristic of Figure 6.

Another variant of the three-layer structure is used for clamping applications of 10 V or less; see Figure 8. Here, the centre P-type layer is lightly doped and thin. When reverse voltage is applied the depletion layer extends completely through the centre layer and contacts the bottom N-type material layer. This action is called "punch-through" [b-King]. Products in the voltage range of 2.5 V to 5 V are commonly available in current ratings of 20 A 8/20 to 100 A 8/20.

Figure 8 – NPN punch-through voltage limiter structure, circuit symbol and electrical characteristics

The structure is unidirectional with only the negative polarity having the low-voltage fold-back characteristic. For this reason, this component often incorporates additional rectifier diodes as shown in Figure 9.

Figure 9 – Punch-through arrays: unidirectional, bidirectional, single bridged and double bridged

#### 7 Characteristics

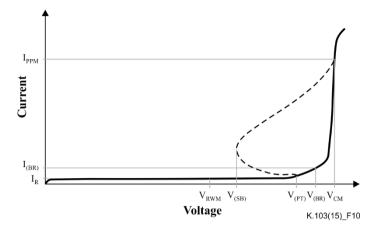

A component electrical characteristic value is measured during a test that applies specified conditions. The key electrical characteristic points of clamping-type voltage limiters are shown in Figure 10. There is a great variation on the terminology used to describe these points. This clause explains the terminology used in this Recommendation and the significance of a parameter.

Figure 10 – Key values on breakdown characteristic

### 7.1 Stand-off or maximum reverse working voltage, V<sub>RWM</sub>

Stand-off or maximum reverse working voltage ( $V_{\text{RWM}}$ ) is the peak value of a normal system working voltage that the component should be used with.

## 7.1.1 Maximum reverse working voltage, V<sub>RWM</sub>

Maximum reverse working voltage ( $V_{RWM}$ ) is the highest instantaneous value of the reverse voltage, including all repetitive transient voltages, but excluding all non-repetitive transient voltages.

## 7.1.2 Reverse current *I*<sub>R</sub>

The total conductive current flowing through the diode when specified reverse voltage is applied is called reverse current ( $I_R$ ). It may also commonly be called leakage current.

The component current,  $I_R$ , is measured when the data sheet specified  $V_{RWM}$  voltage is applied. The data sheet should specify the maximum  $I_R$  value a tested component can have.

A design consideration is the temperature inside the equipment where the component is used (microclimate). In general, the  $I_R$  of a PN junction doubles every 10°C. A temperature increase of 40 K to 65°C will increase  $I_R$  by 2<sup>4</sup> or 16 times. This may be a design consideration for system loading.

The starting point for most designs would be to determine the peak service voltage in normal operation, then select a component with a  $V_{\text{RWM}}$  voltage equal to or greater than the service peak voltage.

## 7.2 Breakdown voltage, V(BR)

This parameter is the voltage level where the components start to conduct significant current, and clipping of the applied voltage begins.

## 7.2.1 Breakdown voltage V(BR)

Breakdown voltage  $(V_{(BR)})$  is the voltage in the region where breakdown occurs.

## 7.2.2 Breakdown current *I*<sub>(BR)</sub>

Breakdown current  $(I_{(BR)})$  is the current in the region where breakdown occurs.

The component breakdown voltage,  $V_{(BR)}$ , is measured when the data sheet specified  $I_{(BR)}$  current is applied. The data sheet should specify the maximum and minimum  $V_{(BR)}$  values a tested component can have.

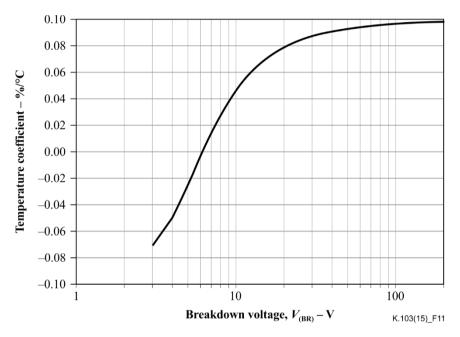

A design consideration is the temperature inside the equipment where the component is used (microclimate). The temperature coefficient of  $V_{(BR)}$  depends on the value of  $V_{(BR)}$ ; see Figure 11. In

general, when  $V_{(BR)}$  is greater than 20 V a coefficient of  $0.1\%/^{\circ}C$  can be assumed. A temperature change of 40 K will cause a 4% change in the  $V_{(BR)}$  value.

Figure 4 shows that there is a considerable difference between the characteristics of 3.6 V, 8.2 V and 15 V breakdown diodes. The reason is that there are two breakdown mechanisms: Zener and avalanche. The 3.6 V diode has Zener breakdown and the characteristic has a high slope resistance. The 15 V diode has avalanche breakdown and the characteristic has a low slope resistance. The 8.2 V diode has a mixture of the two types of breakdown. The initial conduction is due to Zener breakdown, but as the current rises and the voltage increases, the breakdown becomes avalanche. The temperature coefficient characteristic, Figure 11, shows a similar effect. Below 6 V the Zener breakdown negative temperature coefficient predominates and above 6 V the avalanche breakdown positive temperature coefficient predominates. The temperature coefficient is dependent on the value of  $I_{(BR)}$  used for the  $V_{(BR)}$  measurement. Higher values of  $I_{(BR)}$  make the curve more negative. For example, increasing the test current from 5 mA to 40 mA on a 10 V component decreases the temperature coefficient from  $0.05\%/^{\circ}$ C to  $0.03\%/^{\circ}$ C.

Figure 11 – Temperature coefficient of breakdown voltage  $V_{(BR)}$  example

Historically, the Zener breakdown phenomenon was discovered first by C. Zener in 1934 [b-Zener]. It was not until 1953 that it was realised that there was a second form of breakdown phenomenon, avalanche breakdown also existed, as discovered by K.G. McKay and K.B. McAffee [b-McKay]. Due to the longer usage of the terminology, all breakdown diodes are often incorrectly called "Zener diodes".

## 7.3 Clamping voltage, Vc

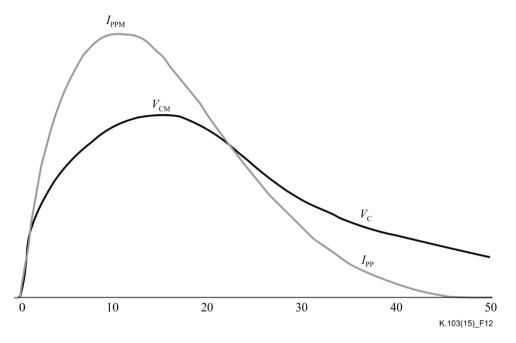

The clamping voltage ( $V_{\rm C}$ ) parameter is the let-through (clamping) voltage of the component during the conduction of a current impulse having a peak pulse current ( $I_{\rm PP}$ ) and specified waveshape. The highest (maximum) value of clamping voltage ( $V_{\rm CM}$ ) occurs at the rated peak (maximum) impulse current ( $I_{\rm PPM}$ ).

## 7.3.1 Maximum clamping voltage, VCM

Maximum clamping voltage ( $V_{CM}$ ) is the peak voltage developed when conducting the rated ( $I_{PPM}$ ) current waveform.

### 7.3.2 Maximum peak pulse current, *I*<sub>PPM</sub>

Maximum peak pulse current ( $I_{PPM}$ ) is the rated value of maximum impulse current that may be applied.

The component  $V_{CM}$  is measured when the data sheet specified  $I_{PPM}$  current is applied. The data sheet should specify the highest  $V_{CM}$  value a tested component can have.

The time at which  $V_{CM}$  occurs will not be at the time at which the impulse reaches  $I_{PPM}$ ; see Figure 12.

Figure 12 – V<sub>C</sub> and I<sub>PP</sub> waveforms

## 7.4 Punch-through voltage V(PT)

The current level at which a fold-back component reaches the punch-through voltage ( $V_{(PT)}$ ) may not be well defined; see Figure 10. For this reason, the best measurement approach is to apply a low-level current ramp and measure the peak voltage. This voltage is equivalent to  $V_{(BR)}$  in a normal breakdown characteristic.

## 7.4.1 Punch-through voltage, V(PT)

Punch-through voltage ( $V_{(PT)}$ ) is the first voltage peak in the low-level current voltage characteristic.

## 7.5 Snap back voltage V(SB)

The current level at which a fold-back component breakdown voltage is at its lowest value (snapback voltage ( $V_{(SB)}$ )) may not be well defined; see Figure 10. For this reason, the best measurement approach is to apply a low-level current ramp and measure the minimum breakdown voltage. If the service being protected has a DC supply it is important that the snapback voltage is higher than the DC supply voltage to avoid the possibility of latch-up at the snapback voltage.

## 7.5.1 snapback voltage, V(SB)

Snapback voltage ( $V_{(SB)}$ ) is the lowest voltage in the breakdown characteristic after the punch-through occurs.

## 7.6 Forward biased PN junction voltage, V<sub>F</sub>

The main parameter for a forward biased PN junction is the forward voltage ( $V_F$ ) at  $I_{PPM}$ .

#### 7.6.1 Forward voltage, V<sub>F</sub>

Forward voltage ( $V_F$ ) [b-IEC 60747-2] is the voltage across the terminals which results from the flow of current in the forward direction.

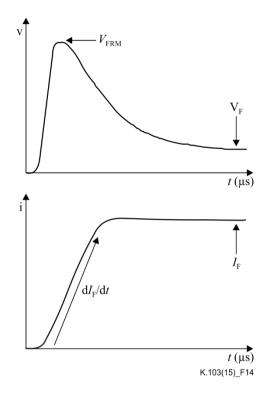

The forward voltage varies with temperature, Figure 13. The typical forward voltage temperature coefficient is  $-2 \text{ mV/}^{\circ}\text{C}$ , falling to about  $-1.3 \text{ mV/}^{\circ}\text{C}$  at high currents.

Figure  $13 - I_F$  vs.  $V_F$  at three temperatures

At fast rates of current rise it can take some time for the PN junction to establish full conduction. This results in a voltage spike at the beginning of conduction, Figure 14. If the forward voltage characteristic is being used to limit voltage to specific levels under impulse conditions the component  $V_{\text{FRM}}$  should be specified. For example, some samples of the commonly used 1N4000 series rectifiers were found to have  $V_{\text{FRM}}$  values of over 100 V when tested with an 8/20 impulse current.

#### 7.6.2 Forward recovery voltage, V<sub>FR</sub>

Forward recovery voltage ( $V_{\text{FR}}$ ) [b-IEC 60747-2] represents the varying voltage occurring during the forward recovery time after instantaneous switching from zero or a specified reverse voltage to a specified forward current.

Figure 14 – Forward recovery voltage vs. time

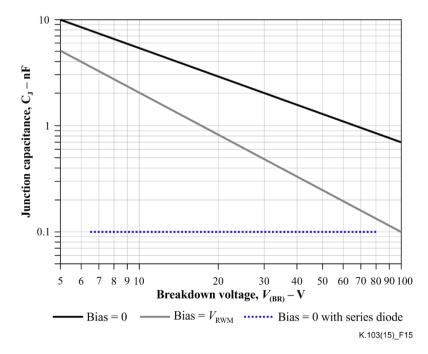

#### 7.7 Junction capacitance, C<sub>J</sub>

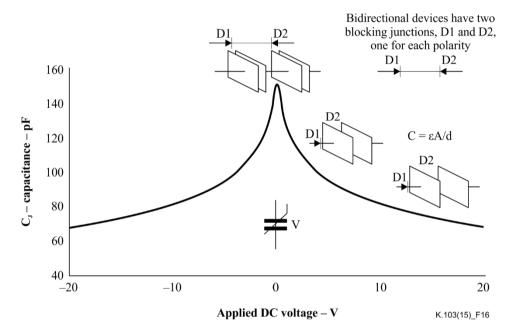

The capacitance of a reverse biased PN junction ( $C_J$ ) decreases with increasing breakdown voltage and the applied voltage. The signal amplitude used to measure capacitance is typically 50 mV rms. This low level is necessary to avoid rectification by the forward characteristic of unidirectional breakdown diodes.

Figure 15 shows how the capacitance of a 1500 W unidirectional diode decreases with increasing  $V_{(BR)}$  and applied DC bias. The dotted 100 pF line is for the same PN structure, but with a series diode to lower the capacitance (extreme left configuration of Figure 5). Low-voltage punch-through components in diode arrays can have capacitance values approaching 10 pF.

Figure 15 – Capacitance variation with  $V_{(BR)}$ , voltage bias and configuration

The component capacitance is a problem in high frequency systems as it represents a shunt to the signal and creates signal distortion due to the capacitance variation with signal voltage and DC bias. Bidirectional diodes are two unidirectional structures in series. As a result, the zero bias capacitance of a bidirectional diode will normally be about 50% of a capacitance of a unidirectional diode.

A three-layer structure with 0 V bias has two PN junctions each with its own depletion layer which forms two capacitors in series; see Figure 16. Applying a DC voltage bias causes one junction to forward bias and the other to reverse bias. As the voltage increases the depletion layer width of the reverse biased junction increases, thus further separating the plates of the depletion layer capacitor. As the plates move apart the capacitance decreases. The capacitance curve shown in Figure 16 peaks at 150 pF and falls to 80 pF with a bias of 10 V.

Figure 16 – Bidirectional NPN structure junction capacitance

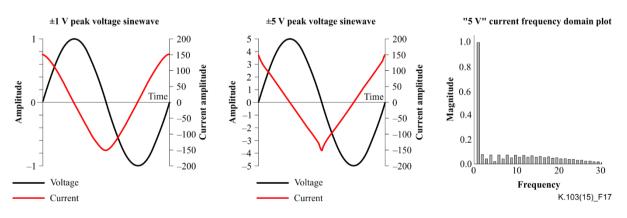

If a sinewave voltage is applied to the component represented by Figure 16, the current drawn will be given by  $i = C_J dv/dt$ . Figure 17 shows the currents for 1 V and 5 V signals. As the voltage passes through zero the capacitance reaches a maximum value and dv/dt is at its fastest rate. With a large 5 V signal, a triangular current waveshape is created due to the zero crossing effect. The triangular current waveshape has a large harmonic spectrum as shown in Figure 17. Multifrequency signals will suffer intermodulation distortion.

Figure 17 – Non-linear capacitance signal distortion

### 7.8 Package inductance

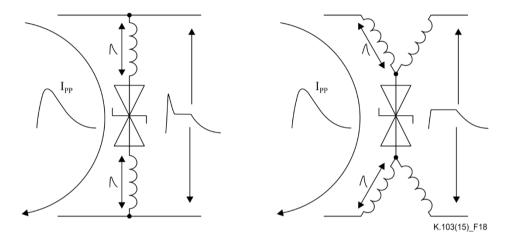

Fast rates of current rise will generate voltage spikes from the component package. Axial leaded components may have package inductance values of 10 nH and surface-mount components may be in the 4 nH ranges. Often the printed circuit wiring will contribute even larger values of inductance. A 20 mm long printed wiring trace could have 25 nH of inductance. A rising current of 100 A/µs would generate a spike of 2.5 V across the trace. In-line package designs and connections considerably reduce these inductive voltage spikes; see Figure 18. The left hand circuit shows how the fast rising current conducted by the breakdown diode creates inductive voltage spikes in the connecting wires; these voltage spikes are also applied to the protected load. The right hand circuit routes the wiring to the diode first then on to the protected load. The load does not have the inductive spike voltages applied to it.

Figure 18 – Reducing inductive spikes by inline connection

#### 8 Ratings

A component electrical rating is verified by applying the rated value and the test check for degradation. Degradation is evaluated by measuring specified electrical characteristic parameters, which should remain within specified limits.

#### 8.1 Peak pulse current, *I*<sub>PP</sub>

The maximum peak pulse current ( $I_{PPM}$ ) and its specified waveshape is the manufacturers' rating that should not be exceeded in service or testing. For components intended to mitigate surges caused by lightning an 8/20 waveshape is usually specified.

#### 8.1.1 Peak pulse current, *I*<sub>PP</sub>

Peak pulse current ( $I_{PP}$ ) is the conducted impulse current of a specified amplitude and waveshape used to determine the clamping voltage  $V_{C}$ .

## 8.1.2 Maximum peak pulse current, IPPM

Maximum peak pulse current ( $I_{PPM}$ ) is the rated maximum value of peak pulse current  $I_{PP}$  that may be applied without causing component failure.

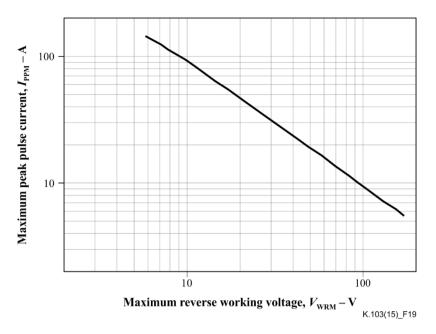

A given component series will use the same sized chip, processed appropriately to give the required voltage. The chip will have a certain energy capability; the energy developed under  $I_{PP}$  conditions will be related to the product of voltage and current. Low-voltage parts will have the highest current rating and high-voltage parts, the lowest current rating; see Figure 19.

Figure 19 – Example plot of *I*<sub>PPM</sub> vs. *V*<sub>WRM</sub>

When operated correctly, breakdown diodes do not have a significant wear-out mechanism. However, when the rated value is exceeded, the diode will either fail instantly or have a short impulse life. In 1977, National Aeronautics and Space Administration (NASA) reported on an impulse durability program for avalanche diodes; see [b-Clark]. The metrics were:

- 12 500 000 pulses applied to the avalanche breakdown diodes;

- 6.8 V, 33 V, 91 V and 190 V parts tested;

- 10/1000 impulse levels of 25%, 50%, 75% and 100% rated current.

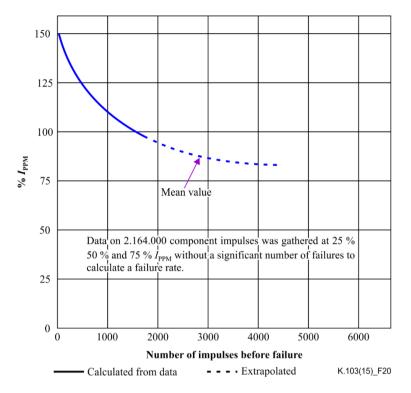

An example result is shown in Figure 20. The result shows that the impulse durability of a breakdown diode depends on how a manufacturer rates the component. At 75%  $I_{PPM}$  and below, testing did not produce any significant number of failures. A 500 impulse life was predicted if 190 V diodes were tested at 125%  $I_{PPM}$  and instant failure at 150%  $I_{PPM}$ .

Figure 20 – 190 V diode per cent of rated peak pulse current vs. mean peak pulses before failure

#### 8.2 Maximum peak pulse power, *P*<sub>PPM</sub>

Figure 12 shows that the impulse peak current and the component maximum voltage may not occur at the same time. The product of the peak current and maximum voltage is called peak pulse power. It is a fictive quantity in so much as the current and voltage may not be coincident in time. Nonetheless, maximum peak pulse power ( $P_{PPM}$ ), is a widely used parameter.

Manufacturers often supply component  $P_{PPM}$  versus pulse width curves for impulse, half sine wave and rectangular pulse waveshapes. For impulse waveshapes of time to half amplitude,  $t_D \mu s$ , the relationship approximates to:

$$y = a(t_D)^{-0.45}$$

where:

y is the ratio of  $P_{PPM}$  at t<sub>D</sub> to the  $P_{PPM}$  at specified component t<sub>D</sub> waveshape, usually 8/20 or 10/1000 a is a constant, 3.8 when the specified component t<sub>D</sub> waveshape is 8/20 and 22 when the specified component t<sub>D</sub> waveshape is 10/1000.

For example, if a component has a specified t<sub>D</sub> waveshape of 10/1000 and the  $P_{PPM}$  value at 8/20 is required,  $y = 22(20)^{-0.45} = 5.7$ . A 500 W  $P_{PPM}$  10/1000 component should have an 8/20 rating in the 5.7 \* 500 = 2850 W region. Working out what this means in terms of  $V_{CM}$  and  $I_{PPM}$  requires the manufacture to supply a relationship curve of these two parameters.

#### 8.3 Power dissipation, *P*<sub>D</sub>

The rated steady state power dissipation ( $P_D$ ) maintains the junction temperature at the highest acceptable value. Values of 175°C or 150°C are typical. If the component is operated in an ambient higher than 25°C, the maximum allowable power loss must be reduced to maintain the same junction temperature. For example, if the maximum junction temperature was 175°C and the ambient was 75°C the maximum power loss becomes  $P_D*(175-75)/(175-25) = 0.67P_D$ . The same derating factor could be applied to the  $P_{PPM}$  rating as well.

#### 9 Application examples

The outline designs presented in this clause are conceptual. The circuit descriptions note some design considerations, but are not rigorous design procedures.

### 9.1 Series connection

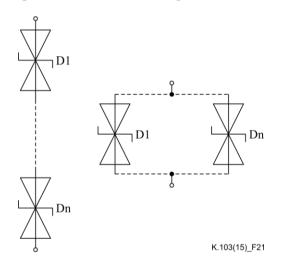

The series connection of several breakdown diodes creates a protective function of higher maximum working voltage,  $V_{RWM}$  voltage than the individual components or a higher maximum peak pulse current,  $I_{PPM}$ , than a single component with the function voltage or both; see Figure 21.

In the following example all the components used in the series string will be of the same type. The series string will have an overall maximum reverse working voltage of  $nV_{RWM}$ , where n is the number of components and  $V_{RWM}$  is the individual component maximum reverse working voltage. The  $I_{PPM}$  of the series string will be the same as the individual string component  $I_{PPM}$ . Figure 19 shows that as the value of  $V_{RWM}$  increases the value of  $I_{PPM}$  decreases.

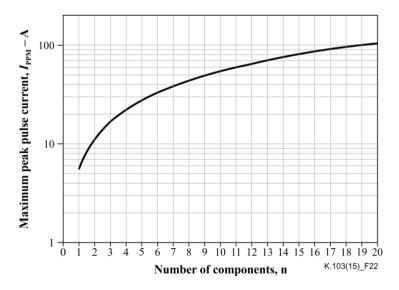

A single component having a  $V_{\text{RWM}}$  of 170 V might have an  $I_{\text{PPM}}$  of 5.5 A, 8/20. Using several lower voltage components in series to make up the same 170 V overall  $V_{\text{RWM}}$  will give a protective function of higher  $I_{\text{PPM}}$ ; see Figure 22. Roughly the  $I_{\text{PPM}}$  of the series string increases by the number of components used for a fixed overall value of  $V_{\text{RWM}}$ . A disadvantage of series connection is that the overall series inductance of the protective function is higher than an individual component.

Figure 21 – Multiple component series and parallel connection

Figure 22 – *I*<sub>PPM</sub> of series string versus number of components n

Lower voltage components have higher  $V_{CM}/V_{RWM}$  ratios. Thus with more components used in the string, not only does the  $I_{PPM}$  increase, but so does the  $V_{CM}$ . This might be undesirable. To have a consistent value of  $V_{CM}$ , the series string  $I_{PPM}$  value needs to be derated.

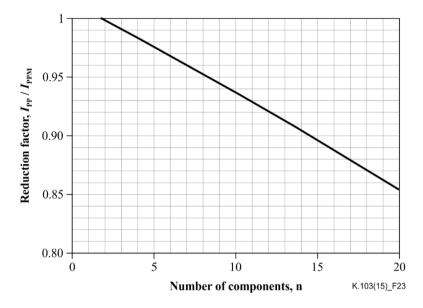

Some manufacturers provide curves of  $V_{\rm C} - V_{\rm (BR)}$  against  $I_{\rm PP}$  and from these the appropriate value of  $I_{\rm PP}$  for a given  $V_{\rm CM}$  can be calculated. Without that information an estimate can be made of the  $I_{\rm PP}$  value from the component  $V_{\rm CM}$ ,  $V_{\rm (BR)}$  and  $V_{\rm RWM}$ . The breakdown characteristic resistance,  $R_{\rm (BR)}$ , is approximated to  $R_{\rm (BR)}=(V_{\rm CM}-V_{\rm (BR)})/I_{\rm PPM}$ . At any current,  $I_{\rm PP}$ , the value of  $V_{\rm C}$  is  $I_{\rm PP} R_{\rm (BR)} + V_{\rm (BR)}$ . The reduction ratio,  $I_{\rm PP}/I_{\rm PPM}$ , is  $(V_{\rm CX} - V_{\rm (BR)})/(V_{\rm CM} - V_{\rm (BR)})$ , where  $V_{\rm CX}$  is the desired value of clamping voltage. Figure 23 shows a smoothed curve of the results obtained for a 1500 W  $P_{\rm PPM}$  component.

#### 9.2 Parallel connection

Paralleling several components or series component strings never realizes the sum of the  $I_{PPM}$  values. Current sharing cannot be guaranteed. Some manufacturers select and match the components used, but that component match can never be exact, so some derating of the ideal  $I_{PPM}$  is necessary. One manufacturer recommends measuring diode  $V_C$  values under moderate (e.g., 1 A) pulse conditions then sorting the diodes into 1% voltage tolerance groups.

One compensating factor for avalanche breakdown diodes is the positive temperature coefficient of voltage. A lower voltage component (or string) will take more current and hence have a higher power loss. This heating raises the junction temperature, which in turn increases the  $V_C$  value. The increased  $V_C$  value causes some of the conducted current to divert to the previously higher  $V_C$  paths.

#### 9.3 DC supply protection

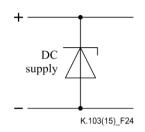

Breakdown diodes, both unidirectional and bidirectional can protect DC supplies from positive and negative transients and provide fault protection. Figure 24 shows the basic arrangement. The breakdown diode,  $V_{\text{RWM}}$ , will be selected to be greater than the highest DC supply voltage value. Positive transients will be limited to the diode  $V_{\text{C}}$  value at the available transient current. Negative transients will be limited to the diode  $V_{\text{F}}$  value at the available transient current.

In some designs the diode will be used as a shorting mechanism if the power supply develops a fault and outputs an excessive voltage. If the faulty power supply causes DC conduction of the diode it will overheat and initially go short, thus terminating the excessive voltage period. This feature only works if the faulty power supply has a limited current and does not cause the failed diode to fuse open. Some manufacturers will provide fusing (opening) information on their diode construction. Example clearing (opening) times published for a 1500 W axial component have been given as 400 A at 0.1 s, 90 A at 10 s and 30 A at 1000 s. With this information a suitable series fuse element can be built into the power supply to operate before the diode fuses open.

Figure 24 – Basic DC supply protection

#### 9.3.1 Automotive load dump

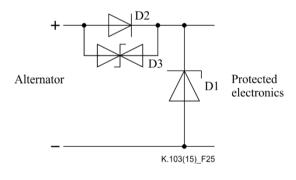

An automotive load dump is the term for the condition when the alternator is charging the battery and the battery becomes disconnected. The resulting alternator energy release results in a voltage spike of about 100 V with a duration in the 300 ms region. Besides making sure that the selected diode, D1, can absorb the load dump energy, automotive load dump protection design has some other considerations. Jumpstarting a car by connecting an external 24 V supply requires that the diode  $V_{\text{RWM}}$  is greater than 24 V. The possibility of a reverse connected battery causing diode forward conduction can be avoided by connecting a series diode, D2. Finally, to avoid reverse polarity voltage spikes breaking down the series diode, a bidirectional breakdown diode, D3, can be added across the series diode, D2. Negative voltage spikes will be limited by the conduction of diodes D3 and D1. This circuit arrangement is shown in Figure 25.

Figure 25 – Automotive load dump protection

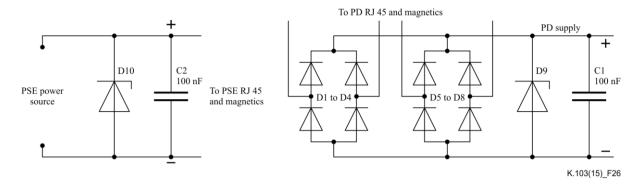

#### 9.3.2 Power over Ethernet (PoE)

In this remote powering system, the power sourcing equipment (PSE) uses the Ethernet cabling to feed a safety extra low voltage (SELV) to the powered device (PD). Traditionally both the PSE and PD contain a 58 V breakdown diode for protection. Figure 26 shows the overvoltage protection of the PSE power feed and the PD power feed recovery circuit. The PSE protection consists of breakdown diode D10 and capacitor C2. The power feed is delivered to the PD by combinations of the four Ethernet twisted pairs, which can operate in mode A or B or both. Diode bridges D1 through D4 and D5 through D8 extract the power feed from the cable connections with the appropriate voltage polarity for the PD power controller. The PSE protection consists of breakdown diode D9 and capacitor C1. The diodes used should be sized for the surge resistibility requirements of the standards to be complied with.

Figure 26 – PSE power feed and PD feed recovery

#### 9.4 **Power frequency protection**

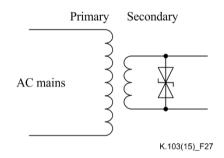

Bidirectional breakdown diodes can protect alternating current (AC) supplies from positive and negative transients. Some AC surge protective devices, SPDs, are made using series and parallel strings of breakdown diodes, see clauses 9.1 and 9.2.

Breakdown diodes do not have the same energy capability as metal-oxide varistor (MOV) protection components and are best placed where the transient is either already limited or has the highest source impedance, which is usually at the protected load. For example, to limit transient voltages, a breakdown diode could be connected across the primary winding or secondary winding of a mains transformer. The secondary winding is preferable as the transformer leakage inductance increases the source impedance of the transient on the secondary side and the protection is applied closest to the load; see Figure 27.

Figure 27 – Placement of breakdown diode on a transformer

## 9.5 Signal protection

There are many types of information and communication technology (ICT) signals. The following clauses provide possible protection schemes for the signal types listed. Each example notes the protection and shows the outline circuit design.

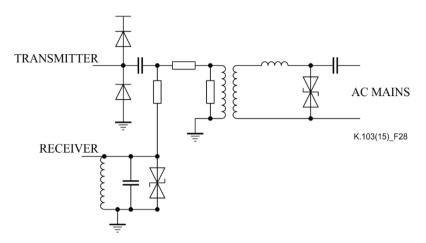

### 9.5.1 Power line communication (PLC) power line coupling

Protection: Two bidirectional breakdown diodes and rectifiers

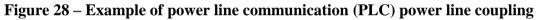

#### 9.5.2 USB 2.0 port

Protection: Double bridged punch-through diode

## 9.5.3 USB 3.0 port

Protection: Triple bridged array with supply clamp and punch-through diode

Figure 30 – Example of USB 3.0 port

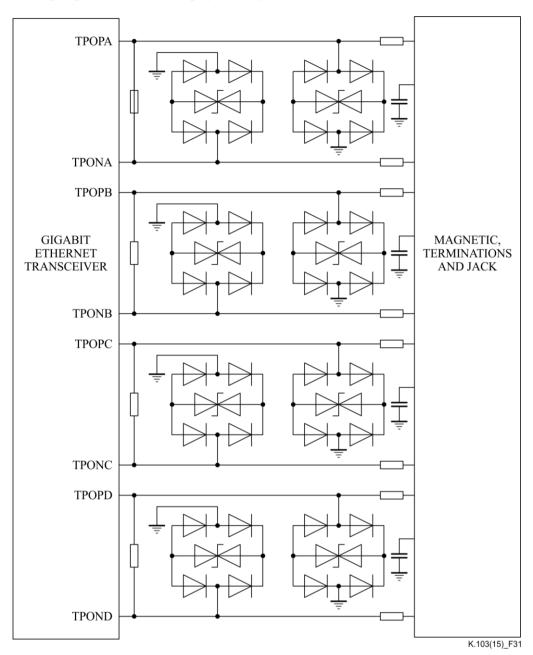

## 9.5.4 Ethernet PHY port

Protection: Bridged protector on each physical layer (PHY) conductor

Figure 31 – Example of Ethernet PHY port

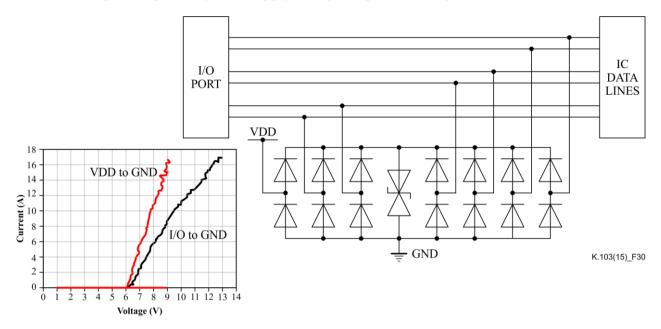

### 9.5.5 IC data lines

Protection: Quadruple bridged, punch-through diode array

Protection: Low capacitance and double bridged protectors

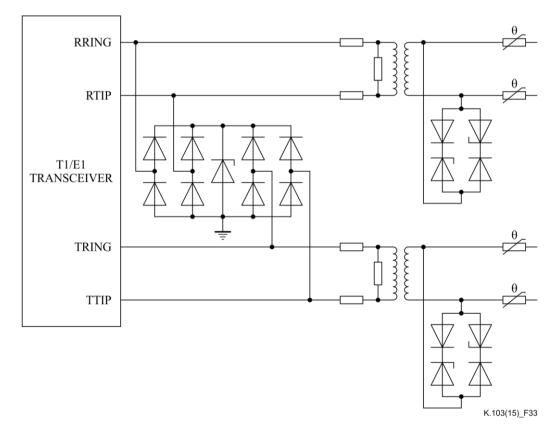

Figure 33 – Example of DS1 (T1/E1/J1) HDSL 4 ports

K.103(15)\_F32

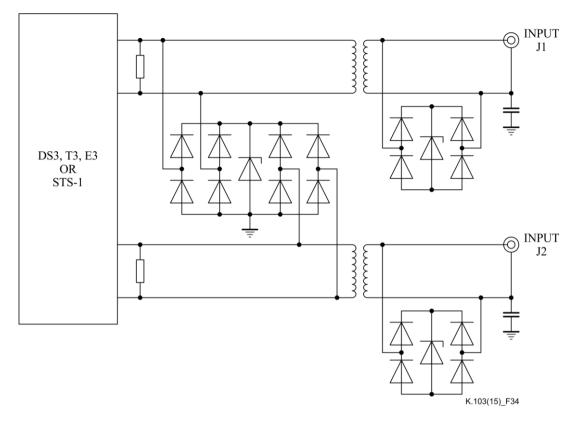

## 9.5.7 DS3 (T3/E3) ports

Protection: Single and double bridged breakdown diodes

Figure 34 – Example of DS3 (T3/E3) ports

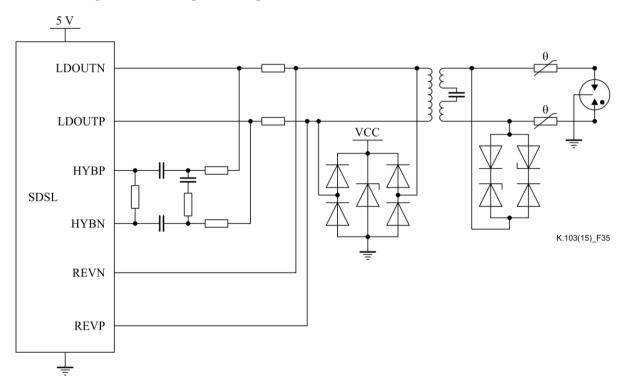

## 9.5.8 Symmetrical digital subscriber line (SDSL) port

Protection: Bridged and low-capacitance protection

Figure 35 – Example of SDSL port

# Bibliography

| [b-ITU-T K.96]    | Recommendation ITU-T K.96 (2014), Surge protective components:<br>Overview of surge mitigation functions and technologies.                                                                                                                                                                    |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [b-IEC 60050-521] | IEC 60050-521 (2002), International Electrotechnical Vocabulary – Part 521:<br>Semiconductor devices and integrated circuits.                                                                                                                                                                 |

| [b-IEC 60664-2-1] | IEC 60664-2-1 (2011), Insulation coordination for equipment within low-voltage systems – Part 2-1: Application guide – Explanation of the application of the IEC 60664 series, dimensioning examples and dielectric testing.                                                                  |

| [b-IEC 60747-2]   | IEC 60747-2 (2000), Semiconductor devices – Discrete devices and integrated circuits – Part 2: Rectifier diodes.                                                                                                                                                                              |

| [b-IEC 61836]     | IEC TS 61836 (2007), Solar photovoltaic energy systems – Terms, definitions and symbols.                                                                                                                                                                                                      |

| [b-Baliga]        | Baliga, B. Jayant (1987), Modern Power Devices, John Wiley & Sons, Inc.                                                                                                                                                                                                                       |

| [b-Clark]         | Clark, O. Melville, (1977), <i>Surge life of transient voltage suppressors, final report</i> , General Semiconductor Industries, Inc. <a href="http://ntrs.nasa.gov/archive/nasa/casi.ntrs.nasa.gov/19780007453.pdf">http://ntrs.nasa.gov/archive/nasa/casi.ntrs.nasa.gov/19780007453.pdf</a> |

| [b-King]          | Ya-Chin King, Bin Yu, Jeff Pohlman and Chenming Hu (1996),<br><i>Punchthrough diode as the transient voltage suppressor for low-voltage electronics</i> , IEEE Transactions on Electron devices, Vol. 43, No. 11, November.                                                                   |

| [b-Lindmayer]     | Lindmayer, J and Wrigley, C.Y. (1966), <i>Fundamentals of Semiconductor Devices</i> , Van Nostrand Company, New York.                                                                                                                                                                         |

| [b-McKay]         | McKay, K.G. and McAffee, K.B. (1953), <i>Electron Multiplication in Silicon and Germanium</i> , Physics Review, Vol. 91, p. 1079.                                                                                                                                                             |

| [b-Zener]         | C. Zener, (1934), <i>A Theory of the Electical Breakdown of Solid Dielectrics</i> ,<br>Proceedings A, Royal Society Publishing (London), Vol. 145, No. 855,<br>p. 523.                                                                                                                        |

## SERIES OF ITU-T RECOMMENDATIONS

| Series A | Organization of the work of ITU-T                                                           |

|----------|---------------------------------------------------------------------------------------------|

| Series D | General tariff principles                                                                   |

| Series E | Overall network operation, telephone service, service operation and human factors           |

| Series F | Non-telephone telecommunication services                                                    |

| Series G | Transmission systems and media, digital systems and networks                                |

| Series H | Audiovisual and multimedia systems                                                          |

| Series I | Integrated services digital network                                                         |

| Series J | Cable networks and transmission of television, sound programme and other multimedia signals |

| Series K | Protection against interference                                                             |

| Series L | Construction, installation and protection of cables and other elements of outside plant     |

| Series M | Telecommunication management, including TMN and network maintenance                         |

| Series N | Maintenance: international sound programme and television transmission circuits             |

| Series O | Specifications of measuring equipment                                                       |

| Series P | Terminals and subjective and objective assessment methods                                   |

| Series Q | Switching and signalling                                                                    |

| Series R | Telegraph transmission                                                                      |

| Series S | Telegraph services terminal equipment                                                       |

| Series T | Terminals for telematic services                                                            |

| Series U | Telegraph switching                                                                         |

| Series V | Data communication over the telephone network                                               |

| Series X | Data networks, open system communications and security                                      |

| Series Y | Global information infrastructure, Internet protocol aspects and next-generation networks   |

| Series Z | Languages and general software aspects for telecommunication systems                        |

|          |                                                                                             |