## ITU-T

TELECOMMUNICATION STANDARDIZATION SECTOR OF ITU G.8261/Y.1361

Amendment 1 (03/2020)

SERIES G: TRANSMISSION SYSTEMS AND MEDIA, DIGITAL SYSTEMS AND NETWORKS

Packet over Transport aspects – Synchronization, quality and availability targets

SERIES Y: GLOBAL INFORMATION INFRASTRUCTURE, INTERNET PROTOCOL ASPECTS, NEXT-GENERATION NETWORKS, INTERNET OF THINGS AND SMART CITIES

Timing and synchronization aspects in packet networks

Amendment 1

-01

Recommendation ITU-T G.8261/Y.1361 (2019) – Amendment 1

### TRANSMISSION SYSTEMS AND MEDIA, DIGITAL SYSTEMS AND NETWORKS

| INTERNATIONAL TELEPHONE CONNECTIONS AND CIRCUITS                                                                                                   | G.100–G.199   |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| GENERAL CHARACTERISTICS COMMON TO ALL ANALOGUE CARRIER-<br>TRANSMISSION SYSTEMS                                                                    | G.200–G.299   |

| INDIVIDUAL CHARACTERISTICS OF INTERNATIONAL CARRIER TELEPHONE<br>SYSTEMS ON METALLIC LINES                                                         | G.300–G.399   |

| GENERAL CHARACTERISTICS OF INTERNATIONAL CARRIER TELEPHONE SYSTEMS<br>ON RADIO-RELAY OR SATELLITE LINKS AND INTERCONNECTION WITH METALLIC<br>LINES | G.400–G.449   |

| COORDINATION OF RADIOTELEPHONY AND LINE TELEPHONY                                                                                                  | G.450-G.499   |

| TRANSMISSION MEDIA AND OPTICAL SYSTEMS CHARACTERISTICS                                                                                             | G.600-G.699   |

| DIGITAL TERMINAL EQUIPMENTS                                                                                                                        | G.700-G.799   |

| DIGITAL NETWORKS                                                                                                                                   | G.800-G.899   |

| DIGITAL SECTIONS AND DIGITAL LINE SYSTEM                                                                                                           | G.900–G.999   |

| MULTIMEDIA QUALITY OF SERVICE AND PERFORMANCE – GENERIC AND USER-<br>RELATED ASPECTS                                                               | G.1000–G.1999 |

| TRANSMISSION MEDIA CHARACTERISTICS                                                                                                                 | G.6000–G.6999 |

| DATA OVER TRANSPORT – GENERIC ASPECTS                                                                                                              | G.7000-G.7999 |

| PACKET OVER TRANSPORT ASPECTS                                                                                                                      | G.8000-G.8999 |

| Ethernet over Transport aspects                                                                                                                    | G.8000-G.8099 |

| MPLS over Transport aspects                                                                                                                        | G.8100-G.8199 |

| Synchronization, quality and availability targets                                                                                                  | G.8200-G.8299 |

| Mobile network transport aspects                                                                                                                   | G.8300-G.8399 |

| Service Management                                                                                                                                 | G.8600–G.8699 |

| ACCESS NETWORKS                                                                                                                                    | G.9000–G.9999 |

|                                                                                                                                                    |               |

For further details, please refer to the list of ITU-T Recommendations.

### Recommendation ITU-T G.8261/Y.1361

### Timing and synchronization aspects in packet networks

### Amendment 1

### **Summary**

Recommendation ITU-T G.8261/Y.1361 defines frequency synchronization aspects in packet networks. It specifies the maximum network limits of jitter and wander that shall not be exceeded. It specifies the minimum equipment tolerance to jitter and wander that shall be provided at the boundary of these packet networks at TDM and synchronization interfaces. It also outlines the minimum requirements for the synchronization function of network elements.

The requirements for the jitter and wander characteristics that are specified in this Recommendation must be adhered to in order to ensure interoperability of equipment produced by different manufacturers and a satisfactory network performance.

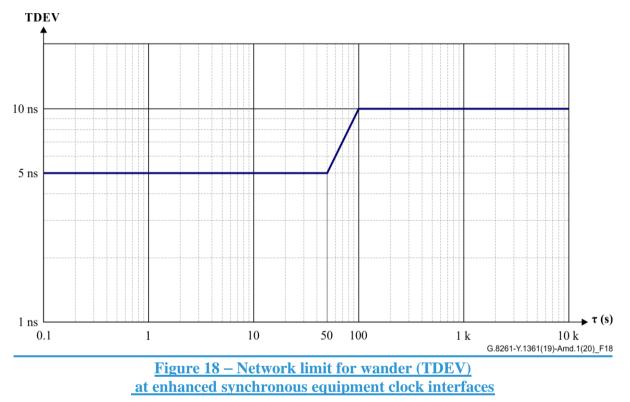

Amendment 1 provides updates for the addition of new TDEV mask to clause 9.2.1.

### History

| Edition | Recommendation                    | Approval   | Study Group | Unique ID*                |

|---------|-----------------------------------|------------|-------------|---------------------------|

| 1.0     | ITU-T G.8261/Y.1361               | 2006-05-22 | 15          | 11.1002/1000/8787         |

| 1.1     | ITU-T G.8261/Y.1361 (2006) Cor. 1 | 2006-12-14 | 15          | 11.1002/1000/9010         |

| 2.0     | ITU-T G.8261/Y.1361               | 2008-04-29 | 15          | <u>11.1002/1000/9416</u>  |

| 2.1     | ITU-T G.8261/Y.1361 (2008) Amd. 1 | 2010-07-29 | 15          | <u>11.1002/1000/10908</u> |

| 3.0     | ITU-T G.8261/Y.1361               | 2013-08-29 | 15          | 11.1002/1000/12015        |

| 3.1     | ITU-T G.8261/Y.1361 (2013) Amd. 1 | 2015-01-13 | 15          | <u>11.1002/1000/12388</u> |

| 3.2     | ITU-T G.8261/Y.1361 (2013) Cor. 1 | 2016-04-13 | 15          | 11.1002/1000/12809        |

| 4.0     | ITU-T G.8261/Y.1361               | 2019-08-29 | 15          | 11.1002/1000/14010        |

| 4.1     | ITU-T G.8261/Y.1361 (2019) Amd. 1 | 2020-03-15 | 15          | 11.1002/1000/14207        |

### Keywords

Circuit emulation, frequency synchronization, packet-based synchronization, synchronous Ethernet.

<sup>\*</sup> To access the Recommendation, type the URL http://handle.itu.int/ in the address field of your web browser, followed by the Recommendation's unique ID. For example, <u>http://handle.itu.int/11.1002/1000/11</u> <u>830-en</u>.

#### FOREWORD

The International Telecommunication Union (ITU) is the United Nations specialized agency in the field of telecommunications, information and communication technologies (ICTs). The ITU Telecommunication Standardization Sector (ITU-T) is a permanent organ of ITU. ITU-T is responsible for studying technical, operating and tariff questions and issuing Recommendations on them with a view to standardizing telecommunications on a worldwide basis.

The World Telecommunication Standardization Assembly (WTSA), which meets every four years, establishes the topics for study by the ITU-T study groups which, in turn, produce Recommendations on these topics.

The approval of ITU-T Recommendations is covered by the procedure laid down in WTSA Resolution 1.

In some areas of information technology which fall within ITU-T's purview, the necessary standards are prepared on a collaborative basis with ISO and IEC.

#### NOTE

In this Recommendation, the expression "Administration" is used for conciseness to indicate both a telecommunication administration and a recognized operating agency.

Compliance with this Recommendation is voluntary. However, the Recommendation may contain certain mandatory provisions (to ensure, e.g., interoperability or applicability) and compliance with the Recommendation is achieved when all of these mandatory provisions are met. The words "shall" or some other obligatory language such as "must" and the negative equivalents are used to express requirements. The use of such words does not suggest that compliance with the Recommendation is required of any party.

#### INTELLECTUAL PROPERTY RIGHTS

ITU draws attention to the possibility that the practice or implementation of this Recommendation may involve the use of a claimed Intellectual Property Right. ITU takes no position concerning the evidence, validity or applicability of claimed Intellectual Property Rights, whether asserted by ITU members or others outside of the Recommendation development process.

As of the date of approval of this Recommendation, ITU had received notice of intellectual property, protected by patents, which may be required to implement this Recommendation. However, implementers are cautioned that this may not represent the latest information and are therefore strongly urged to consult the TSB patent database at <a href="http://www.itu.int/ITU-T/ipr/">http://www.itu.int/ITU-T/ipr/</a>.

#### © ITU 2020

All rights reserved. No part of this publication may be reproduced, by any means whatsoever, without the prior written permission of ITU.

### **Table of Contents**

### Page

| 1     | Scope      |                                                                                           |  |

|-------|------------|-------------------------------------------------------------------------------------------|--|

| 2     | References |                                                                                           |  |

| 3     | Definiti   | ons                                                                                       |  |

|       | 3.1        | Terms defined elsewhere                                                                   |  |

|       | 3.2        | Terms defined in this Recommendation                                                      |  |

| 4     | Abbrevi    | ations and acronyms                                                                       |  |

| 5     | Convent    | tions                                                                                     |  |

| 6     | General    |                                                                                           |  |

|       | 6.1        | Packet network synchronization requirements                                               |  |

|       | 6.2        | TDM timing requirements                                                                   |  |

|       | 6.3        | Synchronization network engineering in packet networks                                    |  |

|       | 6.4        | Timing requirements at edge versus timing requirements in core networks                   |  |

|       | 6.5        | PNT domain and CES domain                                                                 |  |

| 7     | Referen    | ce timing signal distribution over packet networks (PNT domain) 10                        |  |

|       | 7.1        | Plesiochronous and network synchronous methods                                            |  |

|       | 7.2        | Packet-based methods                                                                      |  |

| 8     |            | recovery for constant bit rate services transported over packet networks<br>omain)        |  |

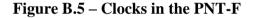

|       | 8.1        | Network synchronous operation                                                             |  |

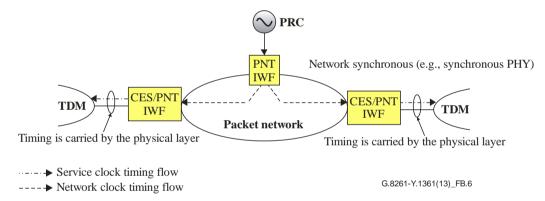

|       | 8.2        | Differential methods                                                                      |  |

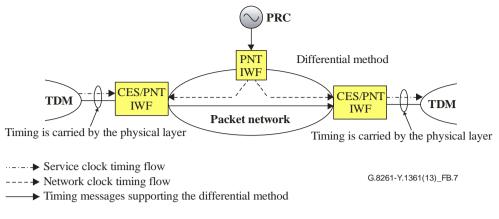

|       | 8.3        | Adaptive methods                                                                          |  |

|       | 8.4        | Reference clock available at the TDM end systems                                          |  |

| 9     | Network    | c limits                                                                                  |  |

|       | 9.1        | CES network limits                                                                        |  |

|       | 9.2        | PNT network limits                                                                        |  |

| 10    | -          | of impairments in the packet network on timing distribution and service covery            |  |

|       | 10.1       | Packet transfer delay and delay variation                                                 |  |

|       | 10.2       | Impacts from packet impairments   32                                                      |  |

| 11    | Impact of  | of the reference clock impairment on the service clock recovery                           |  |

|       | 11.1       | Impairments for the network synchronous operation methods                                 |  |

|       | 11.2       | Impairments for the differential method                                                   |  |

| 12    |            | and consequences of the different synchronization methods over packet<br>reference models |  |

|       | 12.1       | CES domain recommendations                                                                |  |

|       | 12.2       | PNT domain recommendations                                                                |  |

| Anney | x A – Pro  | posed network architecture for synchronous Ethernet                                       |  |

|       | A.1        | PRC Location 40                                                                           |  |

|       |            |                                                                                           |  |

| A.2           | Limiting jitter and wander of synchronous Ethernet                                    |

|---------------|---------------------------------------------------------------------------------------|

| A.3           | Considerations on the design of synchronization network based on synchronous Ethernet |

| A.4           | Example of timing distribution via synchronous Ethernet                               |

| A.5           | Interworking of Ethernet and synchronous Ethernet interfaces                          |

| Annex B – IV  | WF functional partitioning into CES and PNT IWF and network examples                  |

| B.1           | General                                                                               |

| B.2           | IWF clocks                                                                            |

| B.3           | Network examples                                                                      |

| Annex C – C   | ES IWF synchronization related requirements                                           |

| C.1           | Traffic interfaces                                                                    |

| C.2           | Synchronization interfaces                                                            |

| C.3           | IWF synchronization function                                                          |

|               | etwork applications and requirements for clocks specified in ITU-T 2/Y.1362           |

| 11            | Characteristics of Ethernet switches, Ethernet networks, routers and access ologies   |

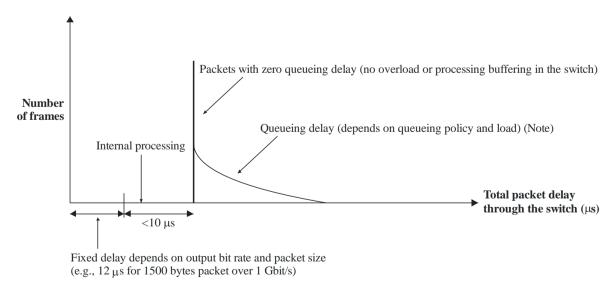

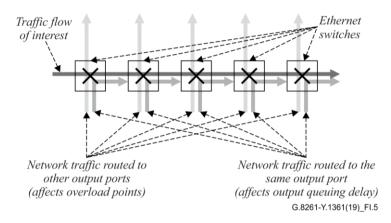

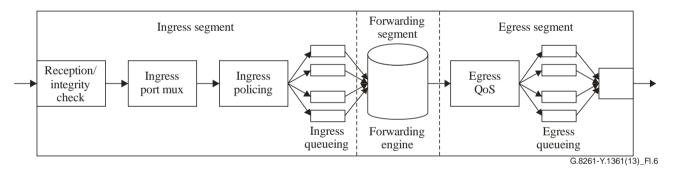

| I.1           | Characteristics of Ethernet switches and networks                                     |

| I.2           | Delay characteristics of routers                                                      |

| I.3           | Delay characteristics of access technologies (Microwave nodes, PON, DSL)              |

| Appendix II - | - Stabilization period                                                                |

| Appendix III  | – Considerations on packet-based methods                                              |

|               | – Applications and use cases                                                          |

|               | Background                                                                            |

| IV.2          | Wireless                                                                              |

| IV.3          | Infrastructure                                                                        |

| IV.4          | Media gateway                                                                         |

| Appendix V -  | - Packet networks reference models                                                    |

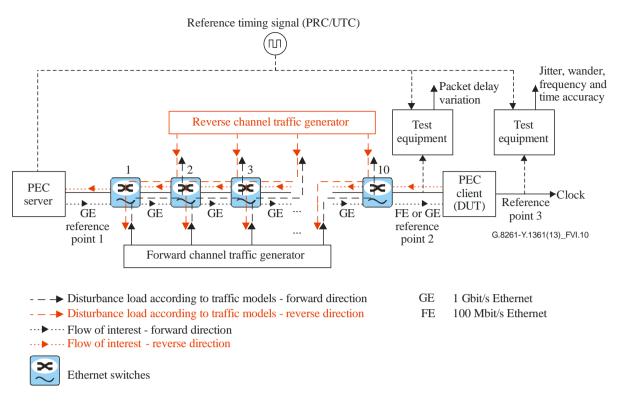

| V.1           | Ethernet networks models                                                              |

| V.2           | Other network models                                                                  |

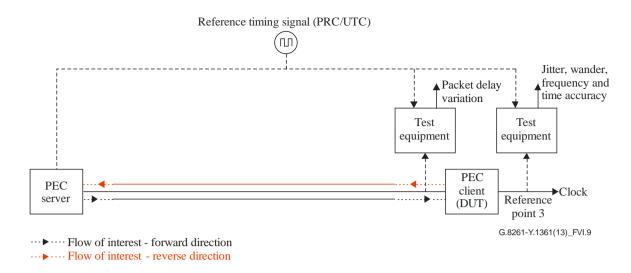

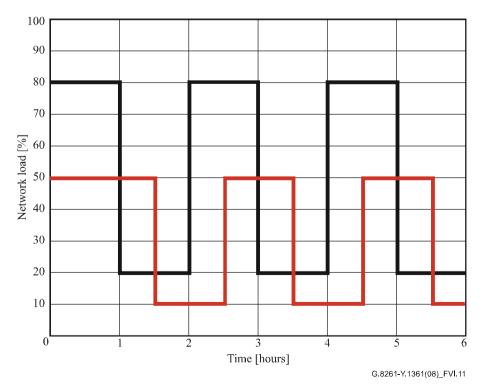

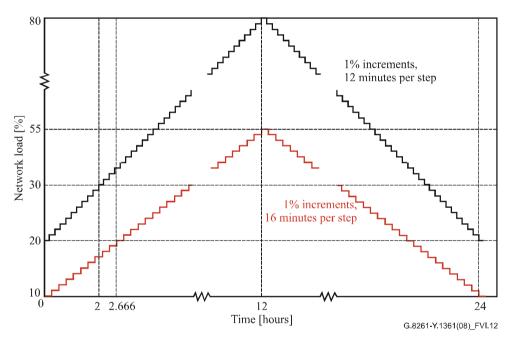

| Appendix VI   | – Measurement guidelines for packet-based methods                                     |

| VI.1          | Measurement reference points                                                          |

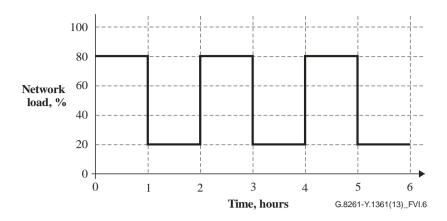

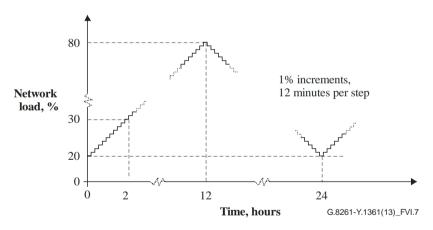

| VI.2          | Input traffic characteristics                                                         |

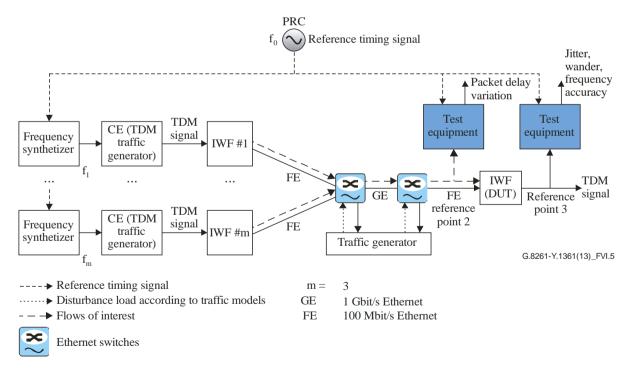

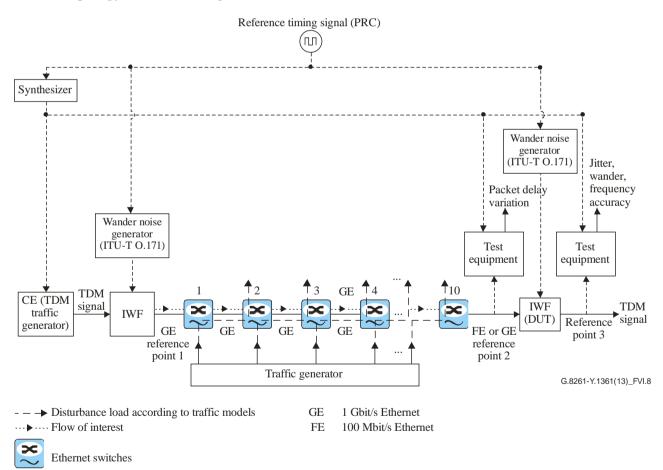

| VI.3          | Test topologies for adaptive methods                                                  |

| VI.4          | Test Topologies for differential methods                                              |

| VI.5          | Test for two-way protocols                                                            |

### Page

| Appendix VII – Wander limits in Deployment Case 1 |         |                                                                                                                                               |     |

|---------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| V                                                 | II.1    | Limits for the 2048 kbit/s interface                                                                                                          | 90  |

| V                                                 | II.2    | Limits for the 1544 kbit/s interface                                                                                                          | 91  |

| Appendix                                          | x VIII  | - Synchronization status messaging in synchronous Ethernet PHY                                                                                | 92  |

| Appendix                                          | x IX –  | IWF examples                                                                                                                                  | 93  |

|                                                   |         | Considerations on measurement of synchronous Ethernet according to nethodologies in comparison with IEEE jitter measurements                  | 96  |

|                                                   |         | Relationship between requirements contained in this Recommendation<br>or key synchronization related Recommendations                          | 97  |

| Appendix                                          | x XII – | - Basic principles of timing over packet networks                                                                                             | 100 |

| Х                                                 | II.1    | General                                                                                                                                       | 100 |

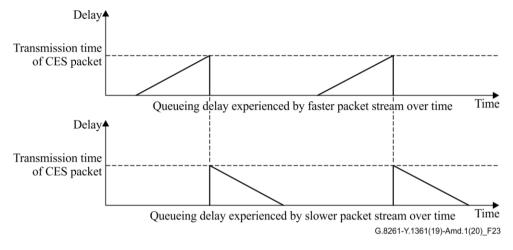

| Х                                                 | II.2    | Packet delay variation mitigation by packet selection                                                                                         | 103 |

| Х                                                 | II.3    | Comparison of packet-based and synchronous PHY methods                                                                                        | 103 |

| Х                                                 | II.4    | Existing standards                                                                                                                            | 104 |

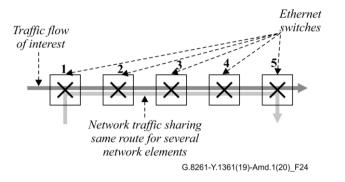

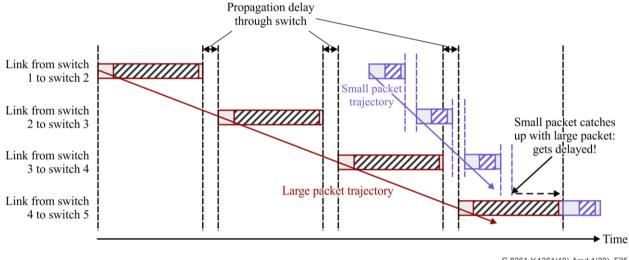

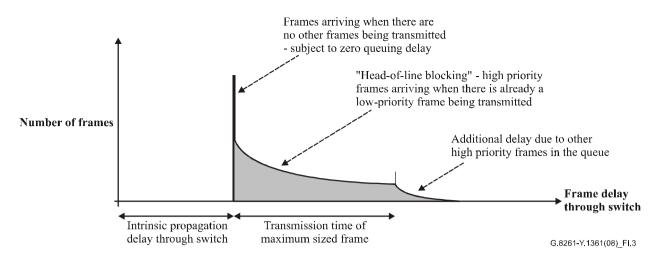

| Appendix                                          | x XIII  | - Evaluation of the packet delay variation generation in a network node                                                                       | 105 |

| Х                                                 | III.1   | Introduction                                                                                                                                  | 105 |

| Х                                                 | III.2   | General considerations                                                                                                                        | 105 |

| Х                                                 | III.3   | General configuration                                                                                                                         | 105 |

|                                                   |         | <ul> <li>Interoperability guidelines for interworking between synchronous<br/>ent clocks and enhanced synchronous equipment clocks</li> </ul> | 107 |

| Bibliogra                                         | aphy    |                                                                                                                                               | 109 |

### Recommendation ITU-T G.8261/Y.1361

### Timing and synchronization aspects in packet networks

### Amendment 1

Editorial note: This is a complete-text publication. Modifications introduced by this amendment are shown in revision marks relative to Recommendation ITU-T G.8261/Y.1361 (2019).

### 1 Scope

This Recommendation defines frequency synchronization aspects in packet networks. It specifies the maximum network limits of jitter and wander that shall not be exceeded. It specifies the minimum equipment tolerance to jitter and wander that shall be provided at the boundary of these packet networks at TDM and synchronization interfaces. It also outlines the minimum requirements for the synchronization function of network elements.

In particular, two main issues are addressed in this Recommendation: the distribution of a synchronization network clock signal over a packet network (PNT domain), and the distribution of a service clock signal over a packet network (CES domain).

NOTE – The application of the transport of SDH signals over packet networks is only partly covered and some aspects are for further study.

The packet networks that are in the scope of this Recommendation are currently limited to the following scenarios:

- Ethernet, ([IEEE 802.3], <u>[IEEE 802.1D<sup>TM</sup>]</u>, and [IEEE 802.1Q<sup>TM</sup>] and [IEEE 802.1Qay<sup>TM</sup>])

- MPLS, [IETF RFC 3031] and [ITU-T G.8110]

- IP<sub>\*</sub> [IETF RFC 791] and [IETF RFC 2460]

The physical layer that is relevant to this Recommendation is the Ethernet media types as defined in [IEEE 802.3]. Other physical layers can be relevant and may be addressed in a future version of this Recommendation.

### 2 References

The following ITU-T Recommendations and other references contain provisions which, through reference in this text, constitute provisions of this Recommendation. At the time of publication, the editions indicated were valid. All Recommendations and other references are subject to revision; users of this Recommendation are therefore encouraged to investigate the possibility of applying the most recent edition of the Recommendations and other references listed below. A list of the currently valid ITU-T Recommendations is regularly published. The reference to a document within this Recommendation does not give it, as a stand-alone document, the status of a Recommendation.

| [ITU-T G.691] | Recommendation ITU-T G.691 (2006), Optical interfaces for single channel STM-64 and other SDH systems with optical amplifiers. |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|

| [ITU-T G.702] | Recommendation ITU-T G.702 (1988), Digital hierarchy bit rates.                                                                |

| [ITU-T G.703] | Recommendation ITU-T G.703 (2016), <i>Physical/electrical characteristics of hierarchical digital interfaces</i> .             |

| [ITU-T G.705] | Recommendation ITU-T G.705 (2000), Characteristics of plesiochronous digital hierarchy (PDH) equipment functional blocks.      |

| [ITU-T G.781] | Recommendation ITU-T G.781 (2017), Synchronization layer functions.                                                            |

| [ITU-T G.803]    | Recommendation ITU-T G.803 (2000), Architecture of transport networks based on the synchronous digital hierarchy (SDH).                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ITU-T G.811]    | Recommendation ITU-T G.811 (1997), <i>Timing characteristics of primary reference clocks</i> .                                                                  |

| [ITU-T G.811.1]  | Recommendation ITU-T G.811.1 (2017), <i>Timing characteristics of enhanced</i> primary reference clocks.                                                        |

| [ITU-T G.812]    | Recommendation ITU-T G.812 (2004), <i>Timing requirements of slave clocks</i> suitable for use as node clocks in synchronization networks.                      |

| [ITU-T G.813]    | Recommendation ITU-T G.813 (2003), <i>Timing characteristics of SDH equipment slave clocks (SEC)</i> .                                                          |

| [ITU-T G.822]    | Recommendation ITU-T G.822 (1988), Controlled slip rate objectives on an international digital connection.                                                      |

| [ITU-T G.823]    | Recommendation ITU-T G.823 (2000), <i>The control of jitter and wander within digital networks which are based on the 2048 kbit/s hierarchy.</i>                |

| [ITU-T G.824]    | Recommendation ITU-T G.824 (2000), <i>The control of jitter and wander within digital networks which are based on the 1544 kbit/s hierarchy.</i>                |

| [ITU-T G.825]    | Recommendation ITU-T G.825 (2000), <i>The control of jitter and wander within digital networks which are based on the synchronous digital hierarchy (SDH)</i> . |

| [ITU-T G.957]    | Recommendation ITU-T G.957 (2006), Optical interfaces for equipments and systems relating to the synchronous digital hierarchy.                                 |

| [ITU-T G.959.1]  | Recommendation ITU-T G.959.1 (2018), Optical transport network physical layer interfaces.                                                                       |

| [ITU-T G.8010]   | Recommendation ITU-T G.8010/Y.1306 (2004), Architecture of Ethernet layer networks.                                                                             |

| [ITU-T G.8013]   | Recommendation ITU-T G.8013/Y.1731 (2015), OAM functions and mechanisms for Ethernet based networks.                                                            |

| [ITU-T G.8110]   | Recommendation ITU-T G.8110/Y.1370 (2005), MPLS layer network architecture.                                                                                     |

| [ITU-T G.8110.1] | Recommendation ITU-T G.8110.1/Y.1370.1 (2011), Architecture of Transport MPLS (T-MPLS) layer network.                                                           |

| [ITU-T G.8251]   | Recommendation ITU-T G.8251 (20012018), <i>The control of jitter and wander within the optical transport network (OTN)</i> .                                    |

| [ITU-T G.8260]   | Recommendation ITU-T G.8260 (20152020), Definitions and terminology for synchronization in packet networks.                                                     |

| [ITU-T G.8261.1] | Recommendation ITU-T G.8261.1/Y1361.1 (2012), Packet delay variation network limits applicable to packet-based methods (Frequency synchronization).             |

| [ITU-T G.8262]   | Recommendation ITU-T G.8262/Y.1362 (2018), <i>Timing characteristics of a synchronous equipment slave clock</i> .                                               |

| [ITU-T G.8262.1] | Recommendation ITU-T G.8262.1/Y.1362.1 (2019), <i>Timing characteristics of</i> an enhanced synchronous equipment slave clock.                                  |

| [ITU-T G.8263]   | Recommendation ITU-T G.8263/Y.1363 (2017), <i>Timing characteristics of packet-based equipment clocks</i> .                                                     |

| [ITU-T G.8264]   | Recommendation ITU-T G.8264/Y.1364 (2017), Distribution of timing information through packet networks.                                                                     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ITU-T G.8265]   | Recommendation ITU-T G.8265/Y.1365 (2010), Architecture and requirements for packet-based frequency delivery.                                                              |

| [ITU-T G.8265.1] | Recommendation ITU-T G.8265.1/Y.1365.1 (2014), Precision time protocol telecom profile for frequency synchronization.                                                      |

| [ITU-T G.8266]   | Recommendation ITU-T G.8266/Y.1376 (2016), <i>Timing characteristics of telecom grandmaster clocks for frequency synchronization</i> .                                     |

| [ITU-T G.8271]   | Recommendation ITU-T G.8271/Y1366 (20172020), Time and phase synchronization aspects of <u>telecommunication</u> packet networks.                                          |

| [ITU-T O.171]    | Recommendation ITU-T O.171 (1997), <i>Timing jitter and wander measuring equipment for digital systems which are based on the plesiochronous digital hierarchy (PDH)</i> . |

| [ITU-T O.172]    | Recommendation ITU-T O.172 (2005), Jitter and wander measuring equipment for digital systems which are based on the synchronous digital hierarchy (SDH).                   |

| [ITU-T Y.1411]   | Recommendation ITU-T Y.1411 (2003), <i>ATM-MPLS network interworking – Cell mode user plane interworking</i> .                                                             |

| [ITU-T Y.1540]   | Recommendation ITU-T Y.1540 (20169), Internet protocol data communication service – IP packet transfer and availability performance parameters.                            |

| [ITU-T Y.1561]   | Recommendation ITU-T Y.1561 (2004), Performance and availability parameters for MPLS networks.                                                                             |

| [IEEE 802]       | IEEE 802-2014, IEEE standard for local and metropolitan area networks:<br>Overview and architecture.                                                                       |

| [IEEE 802.1D]    | IEEE 802.1D-2004, IEEE Standard for local and metropolitan area networks:<br>Media Access Control (MAC) Bridges.                                                           |

| [IEEE 802.1Q]    | IEEE 802.1Q-2018, IEEE Standard for local and metropolitan area networks:<br>Virtual bridged local area networks.                                                          |

| [IEEE 802.3]     | IEEE 802.3-2018, IEEE Standard for Ethernet                                                                                                                                |

| [IETF RFC 791]   | IETF RFC 791 (1981), Internet Protocol (IP).                                                                                                                               |

| [IETF RFC 2460]  | IETF RFC 2460 (1998), Internet Protocol, Version 6 (IPv6) Specification.                                                                                                   |

| [IETF RFC 3031]  | IETF RFC 3031 (2001), Multiprotocol Label Switching Architecture.                                                                                                          |

### 3 Definitions

### **3.1** Terms defined elsewhere

This Recommendation uses the following terms defined elsewhere:

**3.1.1** adaptive clock recovery: See [ITU-T G.8260].

**3.1.2** asynchronous interface: See [ITU-T G.823].

**3.1.3** interworking function (IWF): See [ITU-T Y.1411]. More details and examples are shown in Annex B and Appendix IX.

3.1.4 packet-based method: See [ITU-T G.8260].

- **3.1.5** packet-based method with timing support from the network: See [ITU-T G.8260].

- **3.1.6** packet-based method without timing support from the network: See [ITU-T G.8260].

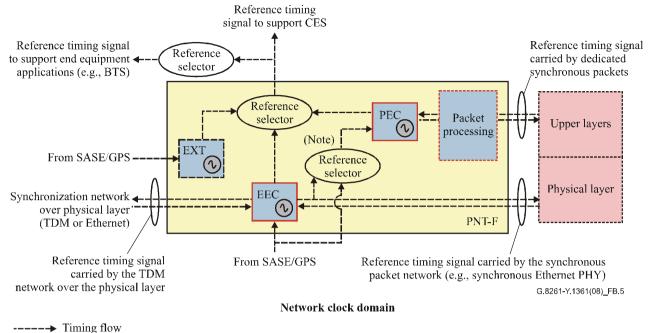

- **3.1.7** packet network timing function (PNT-F): See [ITU-T G.8260].

- **3.1.8** synchronous interface: See [ITU-T G.823].

- **3.1.9 traffic interface**: See [ITU-T G.823].

### **3.2** Terms defined in this Recommendation

This Recommendation defines the following terms:

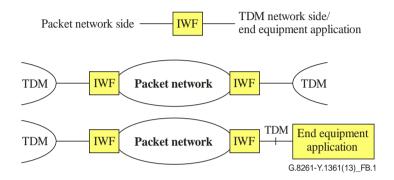

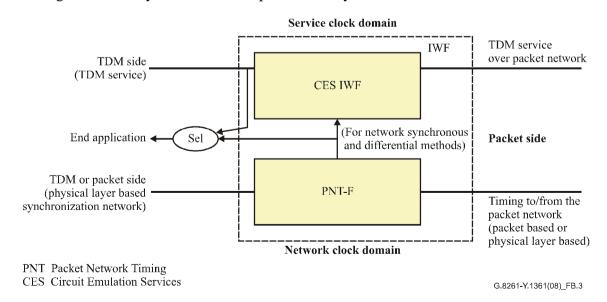

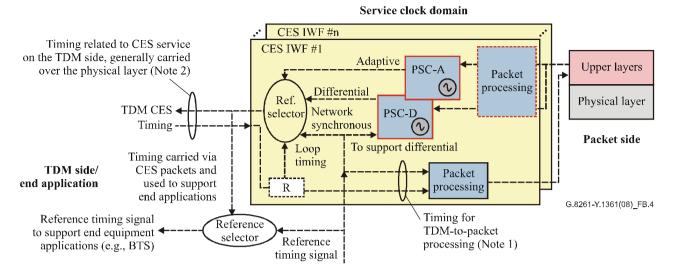

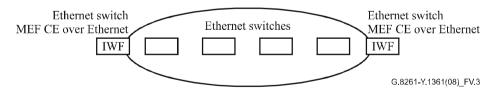

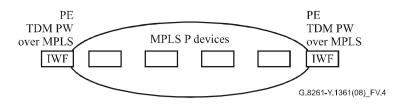

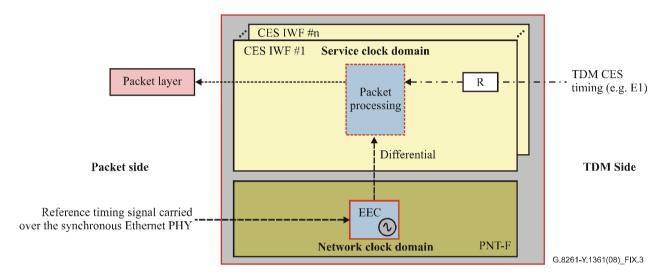

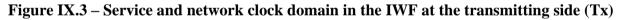

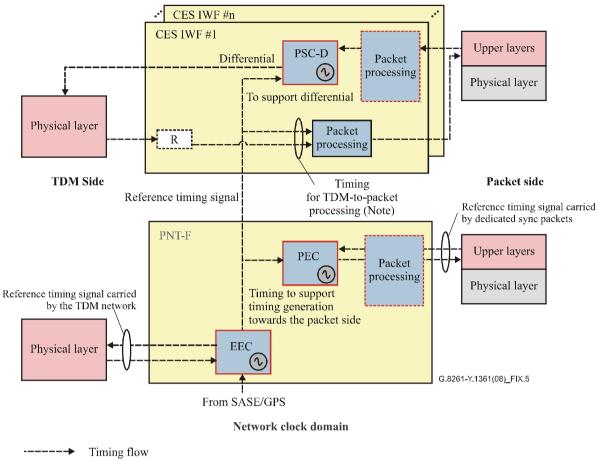

**3.2.1 CES IWF**: The circuit emulation services (CES) interworking function (IWF) is the set of functions within the IWF that supports the service clock domain (see Figure B.3). This includes the function to recover the service clock timing.

**3.2.2** circuit emulation services (CES) island: Segment of a network, based on packet-switched technologies, that emulates either the characteristics of a circuit-switched network or of a PDH/SDH transport network, in order to carry CBR services (e.g., E1).

**3.2.3 enhanced synchronous equipment clock**: A generic term representing the enhanced synchronous equipment clock defined in [ITU-T G.8262.1].

**3.2.4 frequency source traceability**: Frequency source traceability is a relationship where the frequency of all clocks in a system is referenced back to a single physical clock. Under normal operating conditions, all clocks will have the same average frequency in a source-traceable system. Thus, the phase error or maximum time interval error (MTIE) between all clocks in such a system is bounded.

NOTE – A different case is when the clocks have frequency traceability towards accurate master clocks (not necessarily the same pieces of equipment). This is connected to the concept of plesiochronous as defined in [b-ITU-T G.810]. An example is when the clocks have the "PRC traceability" (i.e., traceability to [ITU-T G.811] clocks) in a synchronization network based on the distributed PRC architecture.

**3.2.5** network clock: The clock generating the network clock signal.

**3.2.6** network clock domain: Set of functions dedicated to support the synchronization network (network clock).

**3.2.7 network clock signal**: A reference timing signal that is used as a reference to allow mapping and demapping of a service clock at ingress and egress points of the network respectively. In some applications, the signal could be asynchronous and generated by free running clocks with low requirements in terms of frequency accuracy (e.g., in the Ethernet network, the physical layer can operate up to  $\pm 100$  ppm). In other applications, an accurate reference timing signal is needed. In this case, the signal is typically traceable to a PRC under normal conditions, and the distribution of this signal across the network is accomplished by a synchronization network.

NOTE – For the purpose of this Recommendation, it is assumed that a properly high accurate signal is always involved. Due to that, the network clock signal definition can be considered to coincide with the definition of synchronization network clock signal, and the two terms are used interchangeably throughout this Recommendation.

**3.2.8** network-synchronous operation: Synchronization of the physical layer (usually by a timing distribution of a timing signal traceable to a primary reference clock (PRC), see [ITU-T G.811]).

**3.2.9** service clock: The clock generating the service clock signal.

**3.2.10** service clock domain: Set of functions dedicated to support the CES timing function (service clock).

**3.2.11 service clock signal**: The timing information that is associated with a specific service supported by a network. For instance, in case of E1 TDM service, the timing shall be 2048 kbit/s  $\pm 50$  ppm.

**3.2.12** synchronization network clock: The equipment that provides the timing signal in the synchronization network.

**3.2.13** synchronization network clock signal: The reference timing signal distributed by the synchronization network. This signal is traceable to an accurate master (e.g., PRC).

**3.2.14 synchronous equipment clock**: A generic term representing the SDH equipment clock ([ITU-T G.813]), the Ethernet equipment clock (EEC) and the OTN equipment clock, which are defined in [ITU-T G.8262].

**3.2.15 time division multiplex (TDM)**: A term that conventionally refers to the isochronous bitstreams used in telephony networks; in particular, those belonging to plesiochronous digital hierarchy (PDH) as described in [ITU-T G.705]. The bit rates traditionally used in various regions of the world are detailed in [ITU-T G.702]. Examples of the signals covered by the TDM definition are those belonging to PDH and SDH hierarchies.

**3.2.16** stabilization period: The period beginning at the point in time when a validated timing source has been selected by the IWF and ending when the output timing characteristics are within the output jitter and wander requirements.

**3.2.17** wander budget (of a network island): Wander generated at the output of a network island when an ideal reference timing signal is the input at the first network element of this network island.

### 4 Abbreviations and acronyms

This Recommendation uses the following abbreviations and acronyms:

| 3GPP     | Third Generation Partnership Project          |

|----------|-----------------------------------------------|

| ATM      | Asynchronous Transfer Mode                    |

| BS       | Base Station                                  |

| CBR      | Constant Bit Rate                             |

| CDMA     | Code Division Multiple Access                 |

| CE       | Customer Equipment                            |

| CES      | Circuit Emulation Service                     |

| DUT      | Device Under Test                             |

| EEC      | synchronous Ethernet Equipment Clock          |

| ESMC     | Ethernet Synchronization Messaging Channel    |

| FDD      | Frequency Division Duplex                     |

| FE       | Fast Ethernet                                 |

| GE       | Gigabit Ethernet                              |

| GPS      | Global Positioning System                     |

| GSM      | Global System for Mobile communications       |

| IP       | Internet Protocol                             |

| IP DSLAM | IP Digital Subscriber Line Access Multiplexer |

| IWF      | Interworking Function                         |

| LTE    | Long-Term Evolution                     |  |

|--------|-----------------------------------------|--|

| MAC    | Medium Access Control                   |  |

| M-CMTS | Modular Cable Modem Termination System  |  |

| MPEG   | Moving Picture Experts Group            |  |

| MRTIE  | Maximum Relative Time Interval Error    |  |

| MSAN   | MultiService Access Node                |  |

| MTIE   | Maximum Time Interval Error             |  |

| NR     | New Radio                               |  |

| NTP    | Network Time Protocol                   |  |

| OLT    | Optical Line Termination                |  |

| OTN    | Optical Transport Network               |  |

| PDH    | Plesiochronous Digital Hierarchy        |  |

| PDV    | Packet Delay Variation                  |  |

| PEC    | Packet-based Equipment Clock            |  |

| PHY    | PHYsical (layer)                        |  |

| PNT    | Packet Network Timing                   |  |

| PNT-F  | PNT-Function                            |  |

| PRC    | Primary Reference Clock                 |  |

| PSC-A  | Packet-based Service Clock-Adaptive     |  |

| PSC-D  | Packet-based Service Clock-Differential |  |

| PSTN   | Public Switched Telephone Network       |  |

| PTP    | Precision Time Protocol                 |  |

| QL     | Quality Level                           |  |

| SASE   | Stand Alone Synchronization Equipment   |  |

| SDH    | Synchronous Digital Hierarchy           |  |

| SLA    | Service Level Agreement                 |  |

| SNTP   | Simple Network Time Protocol            |  |

| SRTS   | Synchronous Residual Time Stamp         |  |

| SSM    | Synchronization Status Message          |  |

| SSU    | Synchronization Supply Unit             |  |

| STM    | Synchronous Transfer Mode               |  |

| TCP    | Transmission Control Protocol           |  |

| TDD    | Time Division Duplex                    |  |

| TDEV   | Time DEViation                          |  |

| TDM    | Time Division Multiplex                 |  |

| TDM PW | TDM PseudoWire                          |  |

| ToD    | Time of Day                             |  |

|        |                                         |  |

| UI    | Unit Interval                          |

|-------|----------------------------------------|

| UTC   | Coordinated Universal Time             |

| WCDMA | Wideband Code Division Multiple Access |

### 5 Conventions

The terms "packets" and "frames" are used interchangeably throughout this Recommendation.

Within this Recommendation, the term "Ethernet" refers to an interface as defined in [IEEE 802.3] and that does not comply with the additional timing requirements of synchronous Ethernet as specified in this Recommendation, in [ITU-T G.8262] and in [ITU-T G.8264].

### 6 General

Packet switching was originally introduced to handle asynchronous data.

However, for new applications, such as the transport of time division multiplex (TDM) service and the distribution of synchronization over packet networks, the strict synchronization requirements of those applications must be considered.

The ongoing evolution in telecommunications increases the likelihood of hybrid packet/circuit environments for voice and voiceband data services. These environments combine packet technologies (e.g., asynchronous transfer mode (ATM), IP, Ethernet) with traditional TDM systems. Under these conditions, it is critical to ensure that an acceptable level of quality is maintained (e.g., limited slip rate).

Synchronization in TDM networks is well understood and implemented. Typically, a TDM circuit service provider will maintain a timing distribution network, providing synchronization traceable to a primary reference clock (i.e., clock compliance with [ITU-T G.811]).

The timing and synchronization aspects addressed in this Recommendation are initially concerned with networks with physical layer based on Ethernet media types as defined in [IEEE 802.3] (see Scope, clause 1).

The functional architecture for Ethernet networks is defined in [ITU-T G.8010].

In the context of this Recommendation, the highest layers (e.g., layer 7 in the Open Systems Interconnection (OSI) model) refer to applications transported over the packet networks. Real-time applications have relatively tight timing requirements concerning delay and delay variation. Some applications might resolve their timing issues within higher layers (e.g., MPEG-2); other applications rely on the timing support provided by one or more of the lower layers (e.g., physical layer).

This Recommendation aims at describing different methods to obtain the synchronization-related requirements. Both circuit emulation services (CES) and packet network timing (PNT) domains are considered, and different requirements are described.

Additionally, the requirements for interfaces and equipments that are part of the Ethernet and synchronous Ethernet network are described. It also recommends when to apply different types of synchronization methods.

Some considerations on applicable synchronization requirements in a packet-based network are summarized in the following clauses.

This Recommendation primarily deals with CES in public network environments. In some private network applications involving circuit emulation, it may be sufficient to distribute a non-primary reference clock (PRC) quality level common clock towards CES interworking function (IWF) nodes. However, the use of synchronization timing below PRC quality level could result in interworking

difficulties between different network domains, such as interconnection involving multiple public networks providers.

The use of a non-PRC quality level common clock is for further study.

### 6.1 Packet network synchronization requirements

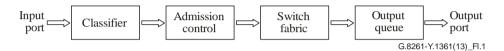

The nodes involved in packet oriented transmission technology (e.g., ATM network nodes) do not require any synchronization for the implementation of the packet switching function. In fact, at any entrance point of a packet switch, an individual device shall provide packet timing adaptation (for instance, cell timing adaptation in case of ATM switch) of the incoming signal to the internal timing. For instance, in the case of ATM networks, the principle to cater for frequency differences is to use idle cell stuffing. Therefore, transmission links, in principle, need not be synchronized with each other.

However, as the packet network evolves to integrate TDM-based applications, i.e., when transporting a constant bit rate (CBR) stream over a packet network and when interworking with public switched telephone network (PSTN) networks, the packet network shall provide correct timing at the traffic interfaces.

This means that the requirements on synchronization functions in packet networks, especially on the boundary of the packet networks, are dependent on the services carried over the network. For TDM based services, the IWF may require network-synchronous operation in order to provide acceptable performance.

### 6.2 TDM timing requirements

The transport of TDM signals through packet networks requires that the signals at the output of the packet network comply with TDM timing requirements. This is crucial to enable interworking with TDM equipment.

These requirements are independent of the type of information (voice or data) transported by the TDM signal.

The adaptation of TDM signals into the packet network is called circuit emulation services (CESs).

The timing requirements that are applicable are: jitter and wander limits at traffic and/or synchronization interfaces, long-term frequency accuracy (which can influence the slip performance), and total delay (which is critical for real-time services, for instance voice service).

### 6.2.1 PDH timing requirements

The plesiochronous digital hierarchy (PDH) timing requirements for traffic interfaces are mainly related to jitter, wander and slip performance.

At the input of the network element at the boundary of a packet network, jitter and wander tolerance requirements apply. At the output of the network element at the egress of the packet network, jitter and wander generation requirements apply.

These values are specified in [ITU-T G.823] for a network based on 2048 kbit/s hierarchy and [ITU-T G.824] for a network based on 1544 kbit/s hierarchy.

In addition, [ITU-T G.822] specifies the applicable slip rate objectives. This is the case when the clock of the equipment that generates the TDM signal and the clock used in the equipment recovering the TDM signal from the packets are different and the slip buffer is needed in the application.

### 6.2.2 Synchronization interfaces requirements

In the case where the PDH signals are defined as synchronization interfaces, the synchronization requirements are more stringent than those for the 2048 kbit/s and 1544 kbit/s traffic interfaces. The

### 8 Rec. ITU-T G.8261/Y.1361 (2019)/Amd.1 (03/2020)

synchronization interface requirements for PDH interfaces are also defined in [ITU-T G.823] and [ITU-T G.824].

### 6.2.3 SDH timing requirements

Any synchronous transfer mode (STM)-N signal must be compliant with [ITU-T G.825]. The relevant requirements refer to the jitter and wander tolerance applicable at the input of the network element at the boundary of a packet network that receives the STM-N data, and jitter and wander generation applicable at the output of the network element generating STM-N traffic at the other end of the packet network.

In the case of STM-N signals, there are no distinctions between traffic and synchronization interfaces as all STM-N signals are defined as synchronization interfaces.

### 6.3 Synchronization network engineering in packet networks

The driving force for much of this work is to provide for the synchronization needs of the application or, in general, the need of certain technologies (such as base stations in global system for mobile communications (GSM) and wideband code division multiple access (WCDMA) networks). In order to achieve such a goal, operators have to distribute a reference timing signal of suitable quality to the network elements processing the application.

One approach is to follow a distributed PRC strategy (e.g., by means of global positioning system (GPS) technologies). An alternative approach is based on a master-slave strategy. The engineering rules for designing the synchronization network in these cases are well understood and documented (e.g., see [ITU-T G.803]) when the underlying transport of the packets (e.g., Ethernet frames) runs over the existing synchronous technologies (PDH or synchronous digital hierarchy (SDH) networks). On the other hand, when the underlying transport is based on non-synchronous technologies (i.e., Ethernet) alternative approaches shall be considered. This is further analysed in clause 7.

### 6.4 Timing requirements at edge versus timing requirements in core networks

Different performances can be requested in case the packet network is part of an access network or is the underlying layer of the core network.

The distribution of a synchronization reference over a portion of a core network may be requested to comply with strict jitter and wander requirements (i.e., [ITU-T G.823], [ITU-T G.824] for synchronization interfaces and [ITU-T G.825]).

On the other hand, in an access network, requirements may be relaxed to allow a distribution of a timing reference signal with performance sufficient (e.g., lower than PRC quality level) to support the timing requirements of the end node (for instance, a base station, or an ITU-T V.90 modem). More information is provided in Appendix IV.

### 6.5 PNT domain and CES domain

This Recommendation addresses two main different issues:

- 1) how to carry a synchronization network clock signal over a packet network:

- this issue is related to the PNT domain, and refers to the network clock (see definitions).

- guidance regarding this issue is provided in clause 7.

- 2) how to carry a service clock signal:

- this issue is related to the CES domain, and refers to the service clock (see definitions).

- guidance regarding this issue is provided in clause 8.

Additional information regarding PNT and CES domains is provided in Annex B.

### 7 Reference timing signal distribution over packet networks (PNT domain)

In order to fulfil the applicable synchronization requirements, it should be possible to distribute a reference timing signal with proper phase stability and frequency accuracy characteristics.

Two main classes of methods are identified in this Recommendation:

- 1) plesiochronous and network synchronous methods (i.e., reference timing signal distributed over the synchronous physical layer).

- 2) packet-based methods.

### 7.1 Plesiochronous and network synchronous methods

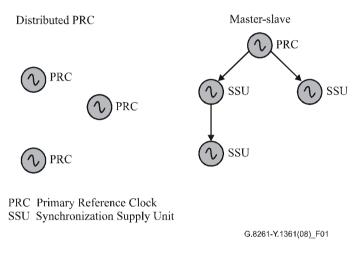

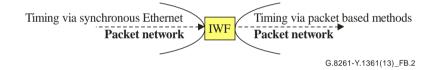

The first class of methods refers to the PRC distributed method (for instance, based on GPS), or the master-slave method using a synchronous physical layer (e.g., STM-N), see Figure 1. These methods are widely implemented to synchronize the TDM networks.

**Figure 1 – Distributed PRC and master-slave methods**

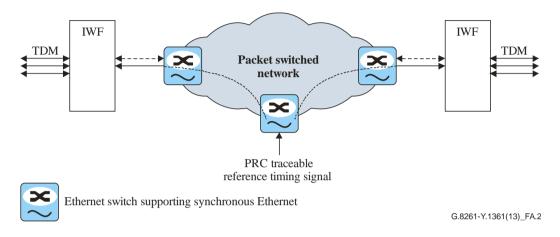

Ethernet networks are free-running ( $\pm 100$  ppm). However, in case of synchronous Ethernet, it is possible to design a master-slave synchronization architecture at the physical layer. In this case, the physical layer can be used to provide reference timing signal distribution over packet networks, from backbone level to access level. This method can also be used to provide timing recovery at the IWFs for CBR services transported over packet networks (network synchronous operations). It could also be used to provide a reference timing signal down to edge access equipment in a pure Ethernet network supporting synchronous Ethernet.

Clause 7.1.1 details a high-level method of achieving a synchronous Ethernet network.

### 7.1.1 Synchronous Ethernet networks

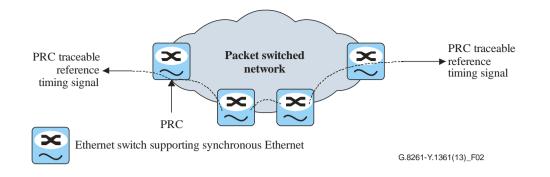

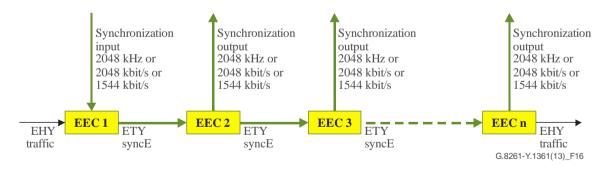

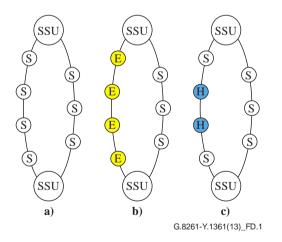

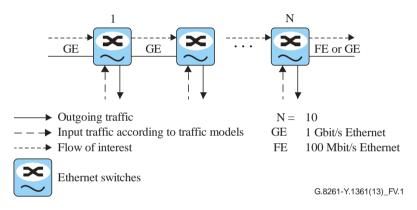

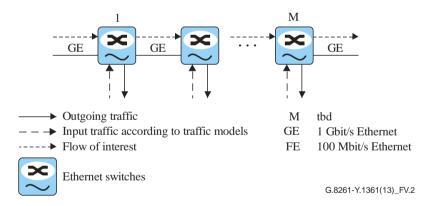

The general concept of delivering a physical layer clock from the Ethernet switch over the synchronous Ethernet is given in Figure 2.

A reference timing signal traceable to a PRC is injected into the Ethernet switch using an external clock port. This signal is extracted and processed via a synchronization function before injecting timing onto the Ethernet bitstream. The synchronization function provides filtering and may require holdover. The clock supporting synchronous Ethernet networks is called synchronous Ethernet equipment clock (EEC), see [ITU-T G.8262].

As shown in the figure, there may be a number of Ethernet switches involved in the distribution of the reference timing signal. In such cases, the synchronization function within these Ethernet switches must be able to recover synchronization "line timing" from the incoming bitstream.

### Figure 2 – Example of master-slave synchronization network over synchronous Ethernet

As part of the architecture, a distinction should be made between the network clock and the service clock as described below.

The term synchronous Ethernet applies to the network clock that controls the bit rate leaving the Ethernet switch. This clock shall comply with [ITU-T G.8262].

Within existing Ethernet technology, the service is effectively asynchronous. In synchronous Ethernet, existing Ethernet services will continue to be mapped into and out of the Ethernet physical layer at the appropriate rates as generated by the service clocks.

A proposed architecture for the synchronization networks based on synchronous Ethernet is described in Annex A.

NOTE – The synchronous Ethernet equipments have to comply with [ITU-T G.781] that specifies the synchronization layer, and [ITU-T G.8264] that specifies the synchronization status message (SSM) for synchronous Ethernet.

### 7.2 Packet-based methods

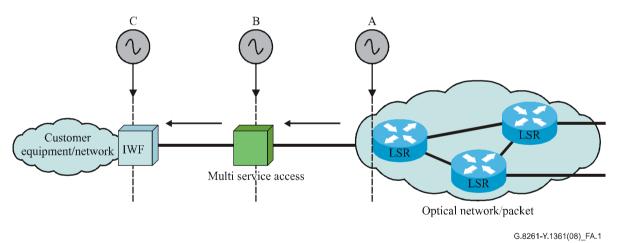

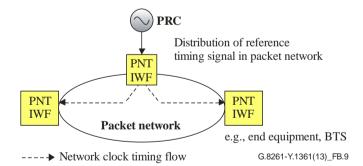

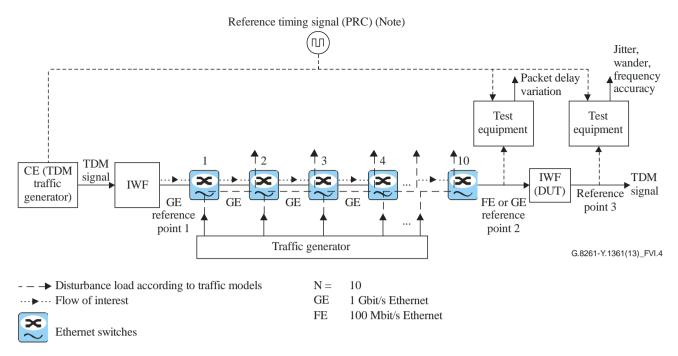

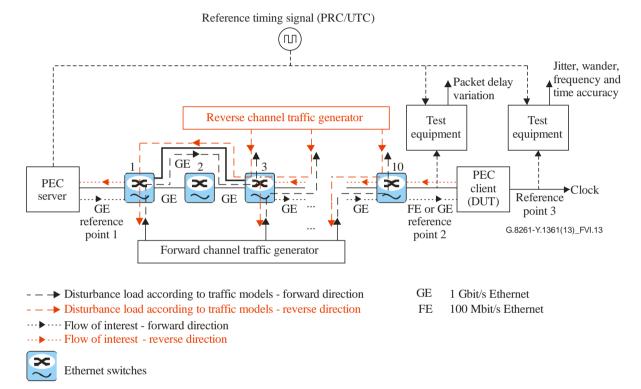

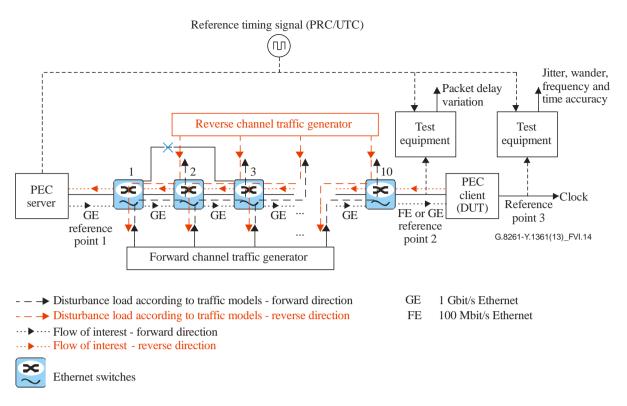

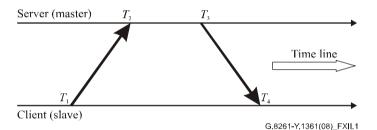

The second class of methods relies on timing information carried by the packets. In this case, the timing could be carried by dedicated time stamp messages as shown in Figure 3. In case the physical layer is not synchronous, this is the only alternative to a PRC distributed approach. The principles underlying such methods are outlined in Appendix XII.

The time stamp can be based on several protocols. Examples of protocols are network time protocol (NTP) and precision time protocol (PTP) (see clause XII.4).

The PTP protocol uses time stamps for synchronizing clocks in the network in a master-slave hierarchy. It can be used to distribute frequency and/or time of day (ToD) information. PTP was originally introduced for Industrial Automation and Test and Measurement Industries; however, a new version (see clause XII.4) has included several updates to allow it to be used for Telecom.

NTP and simple network time protocol (SNTP) are protocols traditionally used to distribute time of day information. The same packets may be used to distribute frequency information as well.

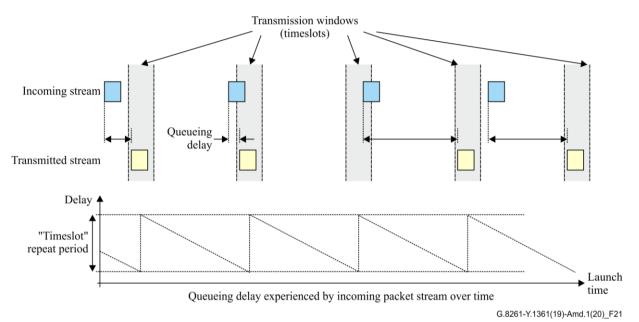

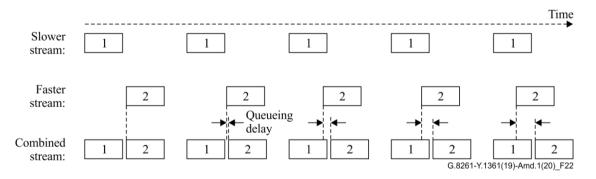

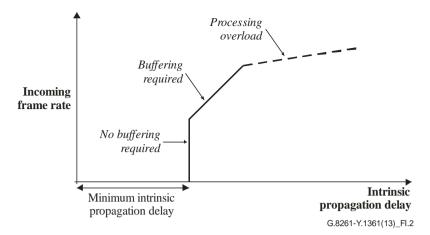

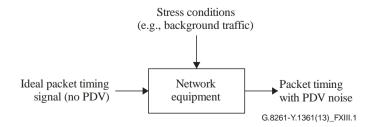

Packet-based methods are adaptive in nature, since they do not require the support of a network-wide synchronization reference. Therefore, performance is impacted by packet delay variation in the network (see clause 10). In order to minimize the impact from the packet network using either PTP or NTP packets, specific algorithms may need to be implemented at the client side, depending on the required accuracy (see Appendices III and IV).

Additional requirements on the intermediate nodes in the network can be considered to enhance the performance of these methods. It should be noted that, especially in cases where legacy equipment is used, this may not always be feasible.

### Figure 3 – Example of packet-based methods with timing distribution of the reference timing signal via time stamps

NOTE – For further details on packet-based methods and related requirements refer to [ITU-T G.8261.1], [ITU-T G.8263], [ITU-T G.8265] and [ITU-T G.8265.1]. Additional information and related Recommendations on packet-based methods are provided in clause 12.2.2.

The clock supporting packet-based methods is called packet-based equipment clock (PEC), (see Annex B).

### 8 Timing recovery for constant bit rate services transported over packet networks (CES domain)

CBR services (e.g., circuit emulated TDM signal) require that the timing of the signal is similar on both ends of the packet network (CES domain) and is handled by the IWF responsible for delivering the constant bit rate stream. The notion of service clock preservation is that the incoming service clock frequency be replicated as the outgoing service clock frequency when considered in terms of a long-term average. It does not imply that wander on the incoming TDM signal be replicated on the outgoing TDM signal.

The four operating methods identified within this Recommendation are described in the following clauses:

- 1) network synchronous operation

- 2) differential methods

- 3) adaptive methods

- 4) reference clock available at the TDM end systems.

### 8.1 Network synchronous operation

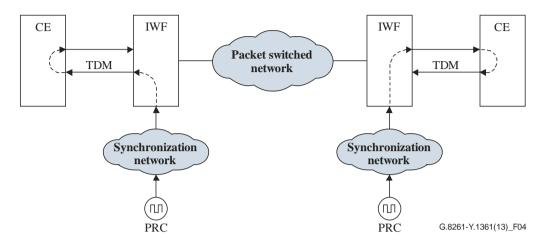

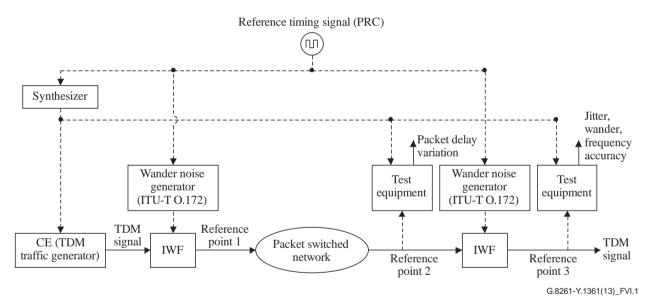

This method refers to the fully network-synchronous operation by using a PRC traceable network derived clock or a local PRC (e.g., GPS) as the service clock (see Figure 4). This implies the availability of a PRC reference. It should be highlighted that this method does not preserve the service timing.

The two PRCs may also originate from the same source.

### Figure 4 – Example of network synchronous operation

NOTE – The reference timing signal at the input to the IWF shall comply with synchronization interfaces as defined in [ITU-T G.823] and [ITU-T G.824].

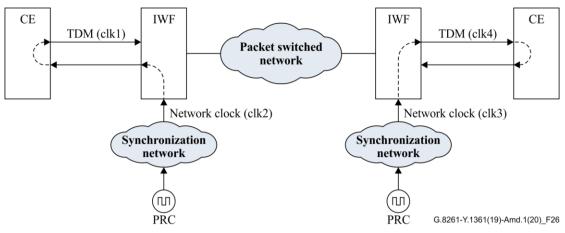

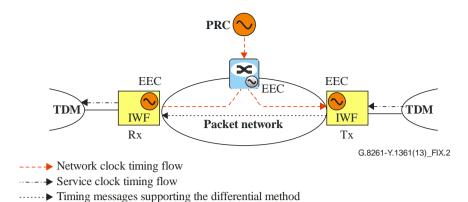

### 8.2 Differential methods

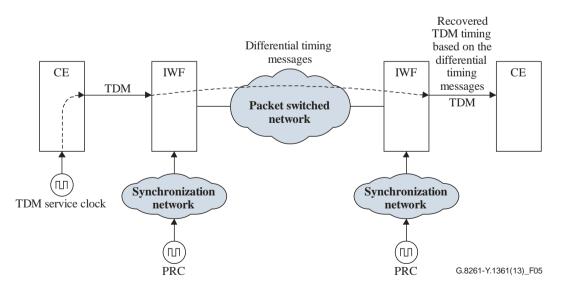

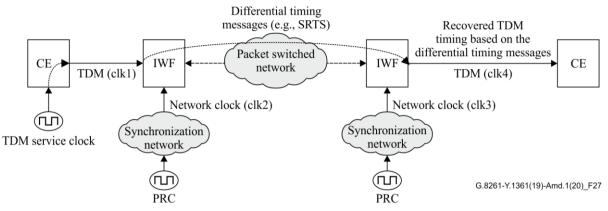

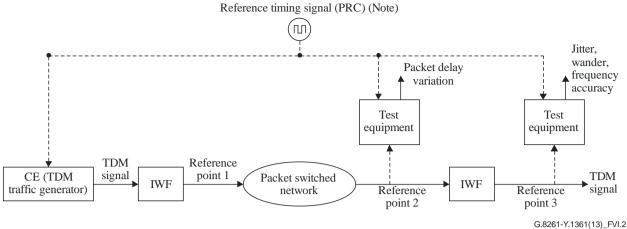

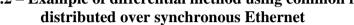

According to the differential methods, the difference between the service clock and the reference clock is encoded and transmitted across the packet network (see Figure 5). The service clock is recovered on the far end of the packet network making use of a common reference clock. The synchronous residual time stamp (SRTS) method [b-ITU-T I.363.1] is an example of this family of methods. It should be highlighted that this method can preserve the service timing.

The two PRCs may also originate from the same source.

### Figure 5 – Example of timing recovery operation based on differential methods

NOTE 1 – Differential methods may work with IWF reference clocks that are not PRC traceable. The use of non-PRC traceable clocks is application-dependent and is not within the scope of this Recommendation.

NOTE 2 – The reference timing signal at the input of the IWF shall comply with synchronization interfaces as defined in [ITU-T G.823] and [ITU-T G.824].

### 8.3 Adaptive methods

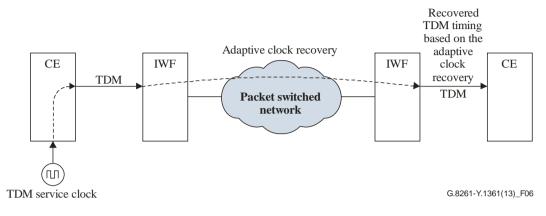

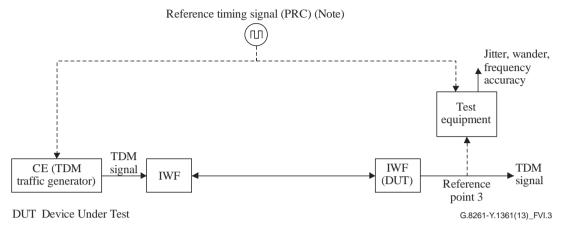

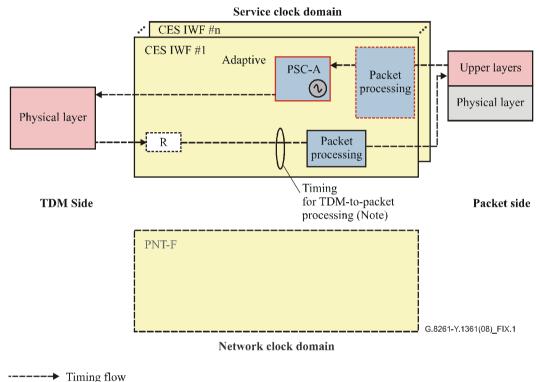

In the adaptive method, the timing can be recovered based on the inter-arrival time of the packets or on the fill level of the jitter buffer. It should be highlighted that this method preserves the service timing (see Figure 6).

Figure 6 – Example of adaptive method

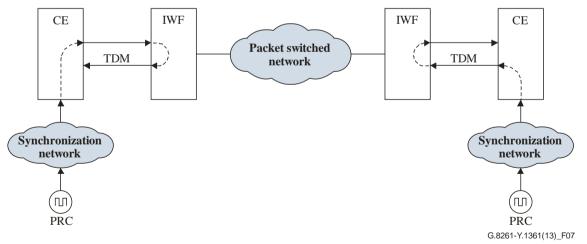

### 8.4 Reference clock available at the TDM end systems

When a reference clock is available at each TDM end system, this is a trivial case, since both the end systems have direct access to a timing reference, and will retime the signal leaving the IWF. Therefore, there is no need to recover the timing.

The use of loop timing in the IWF on the TDM interface is an example of the implementation of this method (see Figure 7). An example, of when this scenario might apply, is when two PSTN domains are connected via a packet network. In this case, both the transmitter and receiver are digital switches where there is a need to control slips.

The two PRCs may also originate from the same source.

### Figure 7 – Example of PRC reference timing signal available at the TDM end systems

### 9 Network limits

### 9.1 CES network limits

The network limits on the TDM links at the output of the CES IWF (output of the Reference selector in the CES IWF in Figure B.4) are defined in this clause.

The jitter and wander network limits currently specified in the relevant ITU-T Recommendations (i.e., [ITU-T G.823] and [ITU-T G.824]) have to be fulfilled in all the scenarios that are relevant for this Recommendation.

This clause describes three different deployment scenarios for a CES segment or island. The jitter and wander limits for TDM traffic interfaces (excluding STM-N signals) carried over the CES segment in each of these scenarios are defined in this clause.

The network limits, applicable to synchronization interfaces (as specified in [ITU-T G.823] and in clause 6 of [ITU-T G.824]) and to STM-N signals carried over packet networks, are for further study.

It should be noted that in some cases, signals with quality, according to clause 5 of [ITU-T G.823] and clause 5 of [ITU-T G.824] (traffic interfaces), when traceable to a PRC, can be used as reference timing signals towards an end equipment able to tolerate these signals and to correctly operate (model for Deployment Case 2 is an example of this scenario).

NOTE – The network limits provided by this clause shall be valid under normal conditions (e.g., when failure conditions or maintenance actions are not present). It is out of the scope of this Recommendation to specify the proportion of time during which these limits apply.

### 9.1.1 Network model underlying the network limits

For the transport of PDH signals, the models in Figure A.1 of [ITU-T G.823] and in Figure A.1 of [ITU-T G.824] are the starting point to consider the insertion of a CES segment. The wander budget allocation for the CES segment must be only a portion of the entire wander budget as specified in [ITU-T G.823] or [ITU-T G.824], since the total wander budget has to be shared with the rest of the network.

Depending on where the CES segment is located, different wander requirements may apply. Several models of CES deployment have been identified; the models are defined in clauses 9.1.1.1, 9.1.1.2 and 9.1.1.3.

NOTE 1 - The figures in this clause do not show the details on how the timing is recovered by the IWF or how the timing is distributed in the packet network. For further details, refer to clauses 7 and 8.

NOTE 2 - Only one CES island is presented in these models, since it aims at allocating wander budget only for the CES technology segment. There might be several CES systems as long as their accumulated wander generation is within the budget allocated for CES.

The wander accumulation through multiple islands is for further study.

### 9.1.1.1 Deployment Case 1

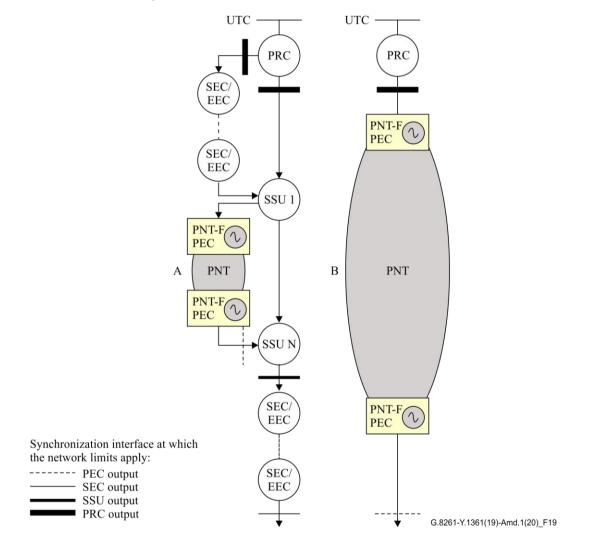

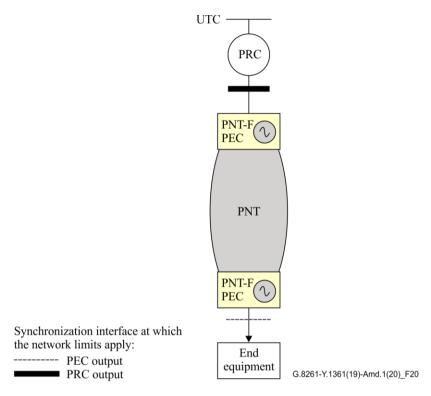

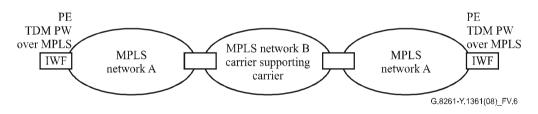

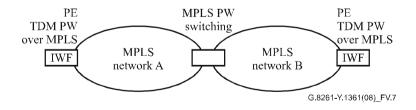

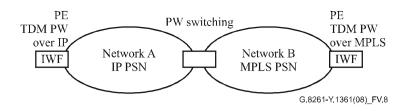

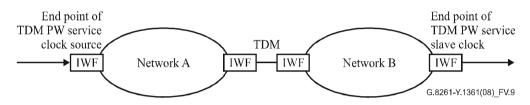

When the CES segment is located at an island between the two switches of the [ITU-T G.823] reference model, the wander budget is calculated based on the model in Figure 8. The model is based on Figure A.1 of [ITU-T G.823] and Figure A.1 of [ITU-T G.824] where one of the SDH islands is replaced by the CES network.

### Figure 8 – Network models for traffic and clock wander accumulation, Deployment Case 1 and Case 2

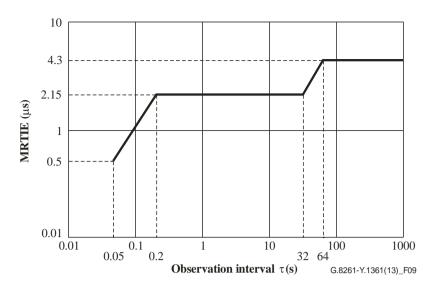

The wander budget, expressed in maximum relative time interval error (MRTIE), for 2048 kbit/s signal is defined in Table 1. The resultant overall specification is illustrated in Figure 9.

| Observation Interval<br>τ (s)                                                                                                                                                                               | MRTIE requirement<br>(µs) |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|

| $0.05 < \tau \le 0.2$                                                                                                                                                                                       | 10.75 τ                   |  |

| $0.2 < \tau \le 32$                                                                                                                                                                                         | 9 × 0.24 = 2.15           |  |

| $32 < \tau \le 64$                                                                                                                                                                                          | 0.067 τ                   |  |

| $64 < \tau \le 1000$                                                                                                                                                                                        | $18 \times 0.24 = 4.3$    |  |

| Note that for the asynchronous configuration, the maximum observation interval to be considered is 80 s.<br>The specification between 80 s and 1000 s for the asynchronous interfaces is for further study. |                           |  |

Table 1 – Deployment Case 1: 2048 kbit/s interface wander budget

Figure 9 – Deployment Case 1: 2048 kbit/s interface wander budget

The 2048 kbit/s jitter network limits shall comply with clause 5.1 of [ITU-T G.823].

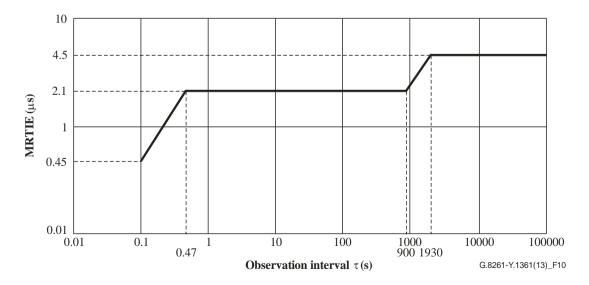

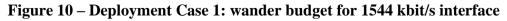

The wander budget, expressed in maximum time interval error (MTIE), for 1544 kbit/s signal is defined in Table 2. The resultant overall specification is illustrated in Figure 10.

| Observation interval (τ)<br>in seconds                | MTIE<br>in μs              |

|-------------------------------------------------------|----------------------------|

| $\tau \le 0.1$                                        | No Requirement (see Note)  |

| $0.1 < \tau \le 0.47$                                 | 4.5 τ                      |

| $0.47 < \tau \leq 900$                                | 2.1                        |

| $900 < \tau \le 1930$                                 | $2.33 	imes 10e^{-3} \tau$ |

| $1930 < \tau \le 86\ 400$                             | 4.5                        |

| NOTE – This region is covered by jitter requirements. |                            |

Table 2 – Deployment Case 1: wander budget for 1544 kbit/s interface

The 1544 kbit/s jitter network limits shall comply with clause 5.1 of [ITU-T G.824].

NOTE – The network limits for the other PDH signals (i.e., 34'368 kbit/s, 44'736 kbit/s and 139'264 kbit/s signals) carried over the CES segments are for further study.

### 9.1.1.2 Deployment Case 2

### Application A

When the CES segment is located outside the network elements containing the slip buffers (see Figure 8), the retiming effect of the switch has to be considered. At the output of this equipment, the timing of the traffic signal will meet the network limit for a synchronization signal which is tighter than for a traffic signal.

The jitter and wander budget of the CES segment in this case is the difference between the 2048 kbit/s network limit (see Figure 1 of [ITU-T G.823]) and the 2048 kbit/s synchronization interface network limit (see Figure 10 of [ITU-T G.823]). The limit, expressed in MRTIE, is provided in Table 3. The resultant overall specification is illustrated in Figure 11.

| Observation Interval<br>τ (s)                                                                                    | MRTIE requirement<br>(μs) |

|------------------------------------------------------------------------------------------------------------------|---------------------------|

| $0.05 < \tau \le 0.2$                                                                                            | 40 τ                      |

| $0.2 < \tau \le 32$                                                                                              | 8                         |

| $32 < \tau \le 64$                                                                                               | 0.25 τ                    |

| $64 < \tau \le 1000 \text{ (Note)}$                                                                              | 16                        |

| Note that for the asynchronous configuration, the maxi<br>The specification between 80 s and 1000 s for the asyn |                           |

Table 3 – Case 2A: 2048 kbit/s interface wander budget

Figure 11 – Case 2A: 2048 kbit/s interface wander budget

In the case of 1544 kbit/s interfaces, Case 1 requirements also apply to Case 2 applications. NOTE 1 – The network limits for the other PDH signals (i.e., 34'368 kbit/s, 44'736 kbit/s and 139'264 kbit/s signals) carried over the CES segments are for further study.

### Application B

In this case, the application recovers timing through the TDM signal; therefore, there is no differential jitter and wander between the clock and the data other than within the bandwidth of the clock recovery since the data and clock are extracted from the same signal. The wander budget of the CES segment is only limited by the timing quality requested by the application (e.g., base station requirements) and not necessarily by [ITU-T G.823].

NOTE 2 - This application is valid only for applications with a single signal; if instead two signals are received, then the jitter and wander for one of those signals may differ from that of the clock extracted from the other signal.

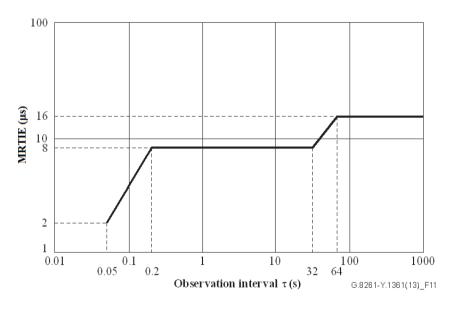

### 9.1.1.3 Deployment Case 3

When retiming is implemented at the output of the SDH islands as shown in Figure 12, the amplitude of noise on the PDH output is that of a synchronization interface. This allows an increase in the wander budget up to that of Deployment Case 2 Application A in some configurations. It should be noted that the service clock is not preserved end-to-end in this case.

Figure 12 – Deployment Case 3 scenario

### 9.2 PNT network limits

The network models and the related network limits are defined separately for the case of the synchronous equipment clocks (e.g., EEC or OEC interfaces) and in the case of the packet-based clocks (PEC interface).

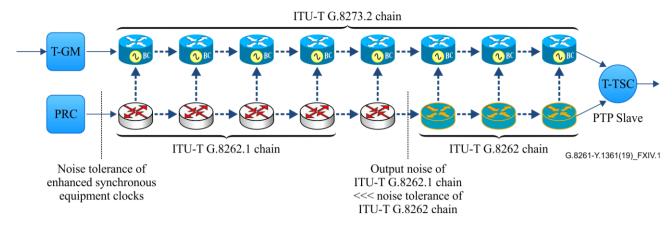

In particular, details on the synchronization chains based on synchronous equipment clocks (e.g., number of the clocks in the synchronization chain) are according to the [ITU-T G.803], [ITU-T G.823] and [ITU-T G.824] models.

Some examples are provided in Figure D.1. As described in these examples, the network limits are defined in order to support hybrid implementations as well, where SDH is mixed with synchronous Ethernet.

NOTE - The network limits provided by this clause shall be valid under normal conditions (e.g., when failure conditions or maintenance actions are not present). It is out of the scope of this Recommendation to specify the proportion of time during which these limits apply.

### 9.2.1 Synchronous equipment clock interface network limits

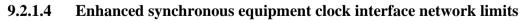

The network limits at the output of synchronous equipment clocks (e.g., EEC and OEC) and enhanced synchronous equipment clocks (e.g., eEEC and eOEC) in a synchronization chain are defined in this clause.

NOTE – These limits are generally applicable at all points in the synchronization network. In some application cases, mainly in the access network, it might be possible to recover timing from an Ethernet signal that is generating jitter and wander according to the tolerance characteristics of the connected equipment (see Appendix IV for examples of relevant applications). The usage of an Ethernet link that does not comply with the limits defined in this clause is the operator's responsibility.

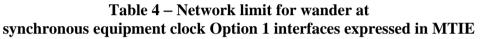

### 9.2.1.1 Synchronous equipment clock Option 1 interface network wander limits

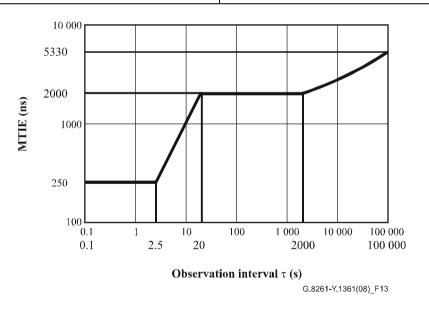

The network limit for wander at the output interface of a synchronous equipment clock (e.g., EEC-1 or OEC-1), expressed in MTIE, is given in Table 4. The resultant overall specification is illustrated in Figure 13.

NOTE – The values are relative to coordinated universal time (UTC), i.e., they include the wander of the PRC.

# Observation interval MTIE requirement (ns) $0.1 < \tau \le 2.5$ 250 $2.5 < \tau \le 20$ 100 $\tau$ $20 < \tau \le 2000$ 2000 $\tau > 2000$ 433 $\tau^{0.2} + 0.01 \tau$

Figure 13 – Network limit for wander (MTIE) at synchronous equipment clock Option 1 interfaces

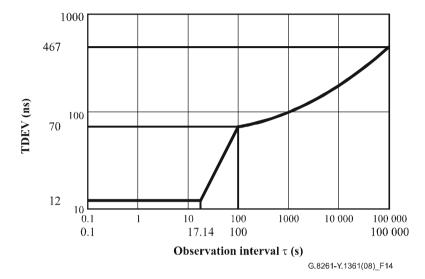

The network limit for wander at the output interface of a synchronous equipment clock Option 1, expressed in Time DEViation (TDEV), is given in Table 5. The resultant overall specification is illustrated in Figure 14.

| Observation interval         | TDEV requirement (ns)                      |

|------------------------------|--------------------------------------------|

| $0.1 < \tau \le 17.14$       | 12                                         |

| $17.14 < \tau \le 100$       | 0.7 τ                                      |

| $100 < \tau \le 1\ 000\ 000$ | $58 + 1.2 \ \tau^{0.5} + 0.000 \ 3 \ \tau$ |

Table 5 – Network limit for wander atsynchronous equipment clock Option 1 interfaces expressed in TDEV

Figure 14 – Network limit for wander (TDEV) at synchronous equipment clock Option 1 interfaces

### 9.2.1.2 Synchronous equipment clock Option 2 interface network wander limits

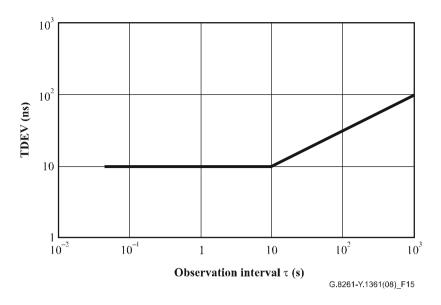

The network limit for wander at the output interface of a synchronous equipment clock Option 2 (e.g., EEC-2, OEC-2), expressed in TDEV, is given in Table 6. The resultant overall specification is illustrated in Figure 15.

| Table 6 – Network limit for wander | (TDEV) at synchronous | s equipment clock Option 2 |

|------------------------------------|-----------------------|----------------------------|

|                                    |                       |                            |

| Observation interval,<br>τ (s) | TDEV<br>(ns)            |

|--------------------------------|-------------------------|

| $0.05 < \tau \le 10$           | 10                      |

| $10 < \tau \le 1000$           | 3.1623 τ <sup>0.5</sup> |

### Figure 15 – Network limit for wander (TDEV) at synchronous equipment clock Option 2 interfaces

The mask in Figure 15 is taken from Figure 5 of [ITU-T G.824]. This mask is also found in Figure I.1 of [ITU-T G.813] for Option 2 network wander limits.

### 9.2.1.3 Synchronous equipment clock interface network jitter limits

See Table 7 for synchronous equipment clock interface network jitter limits.

| Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reference                                                          |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------|

| 2048 kbit/s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | See [ITU-T G.823], clause 6.1: Network limits for output jitter at | (Note 1) |

| 2048 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | synchronization interfaces, SEC requirements                       |          |